MIPI CSI2 Receiver

The Foresys MIPI Core provides a fast path to integrating Image Sensors or other MIPI connected devices into a wide variety of pr…

Overview

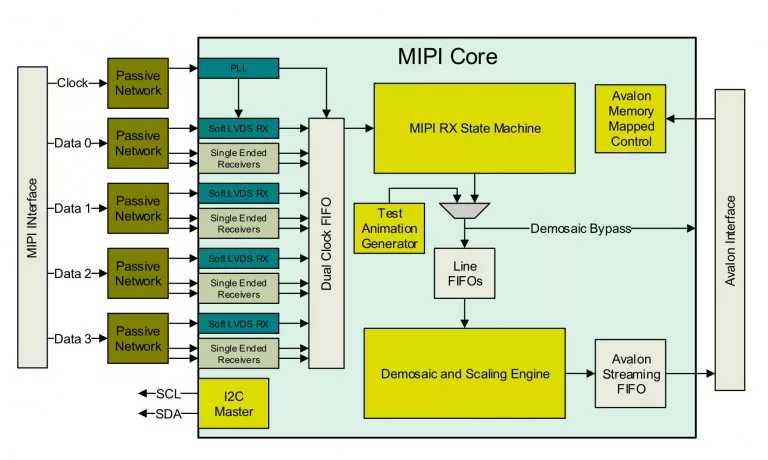

The Foresys MIPI Core provides a fast path to integrating Image Sensors or other MIPI connected devices into a wide variety of products based on Altera devices. The MIPI CSI2 Rx core is designed to convert MIPI data from an image sensor into an Avalon Streaming Video interface.

Key features

- Provides Compatible MIPI D-Phy v1.1 physical layer using FPGA LVDS/LVCMOS IO and passive network

- Supports CSI-2 protocol for unidirectional data transfer

- Compatible with D-PHY Configured for 1 clock and 4 data lanes

- Intended for per-lane clocks rates up to 1 Gbps, depending on device speed grade

- Verifies CSI-2 header ECC field

- Verifies CSI-2 data CRC

- Transmits Avalon Streaming Video

- Optionally converts to 640×480 in RGB_888 format by simultaneously scaling and demosaicing

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about MIPI IP core

MIPI MPHY 6.0: Enabling Next-Generation UFS Performance

MIPI: Powering the Future of Connected Devices

Exploring the Latest Innovations in MIPI D-PHY and MIPI C-PHY

New Developments in MIPI's High-Speed Automotive Sensor Connectivity Framework

Streamlining Camera Security Validation Framework Using Synopsys MIPI CSE v2.0 VIP

Frequently asked questions about MIPI IP cores

What is MIPI CSI2 Receiver?

MIPI CSI2 Receiver is a MIPI IP core from Foresys listed on Semi IP Hub.

How should engineers evaluate this MIPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.