MIPI A-PHY Verification IP

MIPI A-PHY provides an efficient and simple way to verify the MIPI A-PHY.

Overview

MIPI A-PHY provides an efficient and simple way to verify the MIPI A-PHY. The SmartDV Verification IP for MIPI A-PHY is fully compliant with MIPI A-PHY version upto 2.0 Specification and provides the following features.

MIPI A-PHY Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

MIPI A-PHY Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Implemented in native OpenVera, SystemVerilog, Verilog and SystemC.

- Supported RVM, AVM, VMM, OVM, UVM and non-standard verify env.

- Supports MIPI A-PHY specification version upto 2.0.

- Supports single lane and dual lane, point-to-point and serial communication technology.

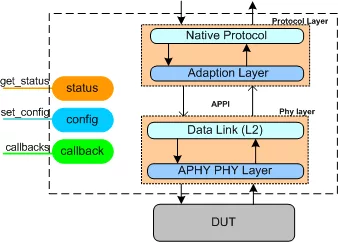

- Supports PHY layer and Data link layer features.

- MIPI A-PHY provides a main unidirectional data stream and a bi-directional low- throughput command and control data stream, and can optionally also deliver the required power supply to peripheral units (i.e., the sensors and/or displays at the edge of the network) directly via the A-PHY data line.

- The model has a rich set of configuration parameters to control MIPI A-PHY functionality.

- Support APPI interface between MIPI A-PHY and Native protocol.

- Support multiple high speed gears (Downlink/Reverse Downlink) ranging from 2Gbps up to 32 Gbps.

- Support multiple low speed gears (Uplink) ranging from 100Mbps up to 1600 Mbps.

- Support 7 discrete Downlink Gears: G1, G2, G3, G4, G5, G6 and G7 and 3 discrete Uplink Gears: U1, U2 and U3

- Support two types of profiles :

- Profile 1 (P1-NRZ 8B/10B)

- Profile 2 (P2 -PAM 4, 8 ,16)

- Support clock recovery, Sink Transmitter shall use the recovered Source clock to generate the proper Sink transmit clock, to reach the proper port rate.

- Support Back-to-Back A-Packets 8B/10B Encapsulation

- Support for below Retransmission types

- RRS (Single Re-transmission)

- GRS (Gap Re-transmission)

- Support Re transmission request / ACK types.

- Support for Fully Paced A-Packet Stream

- Support for ACMD Registers

- Support for ACMP write and Read message in both short and long message format

- Support Scrambler as per specs.

- Support Re-Training sequence.

- Support two types of Startup Procedure:

- Mission Mode startup

- Unidirectional startup

- Support Wake-Up protocol and below Mode of operation :

- Non active Mode

- Active Mode

- Test Mode

- Implements below PHY layer architecture :

- MIPI A-PHY P1 G1/G2 Architecture

- RTS By-Pass Uplink and Downlink

- 8B/10B PCS

- PMD

- MIPI A-PHY P2 G1/G2 Architecture

- RTS for Uplink and Downlink

- 8B/10B PCS

- PMD

- MIPI A-PHY G3-G5 Architecture

- RTS for Uplink, Downlink and Reverse downlink

- 8B/10B PCS for Uplink and Reverse downlink

- PAM 4, 8 ,16 PCS for Downlink and Reverse downlink

- PMD

- Support below Data Link feature:

- Link service

- BIST

- Sleep and Wakeup

- Keep-Alive

- Local function

- Multi-port function

- Network function

- Monitor, Detects and notifies the test bench of significant events such as transactions, warnings, timing and protocol violations.

- Supports constraints Randomization.

- Status counters for various events in bus.

- Callbacks in transmitter and receiver for various events.

- MIPI A-PHY Verification IP comes with complete test suite to test every feature of MIPI A-PHY specification.

- Functional coverage for complete MIPI A-PHY features.

Block Diagram

Benefits

- Faster testbench development and more complete verification of MIPI A-PHY designs.

- Easy to use command interface simplifies testbench control and configuration of Tx,Rx and monitor

- Simplifies results analysis.

- Integrates easily into OpenVera, SystemVerilog, Verilog, SystemC, Specman E.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the MIPI APHY testcases.

- Examples showing how to connect various components, and usage of Tx,Rx and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Video Transport IP core

Introduction to Embedded DisplayPort (eDP) version 1.5

Enabling High Performance SoCs Through Multi-Die Re-use

An HDTV SoC Based on a Mixed Circuit-Switched / NoC Interconnect Architecture (STBus/VSTNoC)

Steps for Delivering Multimedia Over 5 GHz WLANs

Tutorial: The H.264 Scalable Video Codec (SVC)

Frequently asked questions about Video Transport IP cores

What is MIPI A-PHY Verification IP?

MIPI A-PHY Verification IP is a Video Transport IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Video Transport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Transport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.