DisplayPort 2.1 Verification IP

The DisplayPort Verification IP provides an effective & efficient way to verify the DP components of an IP or SoC.

Overview

The DisplayPort Verification IP provides an effective & efficient way to verify the DP components of an IP or SoC. The VIP is fully compliant with DP-2.1 specifications. The VIP is lightweight with easy plug-and-play components so that there is no hit on the design cycle time.

Key features

- Supports Isochronous transport services over the Main-Link.

- Capable Link and device management services over the AUX_CH.

- Can handle AUX transaction to access the DisplayPort Configuration Data (DPCD) address.

- Capable of handling multi stream packet and single stream packet data transmission.

- Supports 128b/132b DPStream Symbol-to-MTP Mapping Rate Control Mandates.

- Supports hot plug and unplug detection and link status failure detection.

- Capable of handling Panel Replay Mode.

- Supports adaptive-Sync Operation for VESA Adaptive Sync.

- Can handle payload bandwidth allocation if stream is added or removed in run time.

- Supports Secondary Data Packets .

- Supports Enhanced and non enhanced Framing mode.

- Capable of handling Video Transmission with following options

- MSA/Ignore MSA Video Timing and/or VSC

- TU generation with and without FEC Encoding/Decoding

- CTA, CVT and DMT Video timing standard

- RGB, YCbCr(444,422,420), ITU-R BT.601, ITU-R BT.709,ITU-R BT.2020, and Adobe RGB colorimetry

- Variable color depth upto 16 bpc.

- Interlaced and progressive video is supported.

- Horizontal Blanking Expansion and Reduced blanking timing as applicable

- Capable of handling various types of Audio on variable frequency, applicable per CTA standard

- LPCM Audio for upto 8 channel

- One bit Audio for upto 8 channel

- 3D LPCM Audio for upto 32 channel

- Supports half duplex mode of operation for aux.

- Connected to link layer through Truechip specific System Interface.

- Supports data width according to the PIPE configuration.

- Maintains link training and Link Status Monitor.

- Supports Reed-Solomon (RS) FEC encoding/decoding as per the specification.

- Supports the scrambling/descrambling process as per the specification.

- Supports 128b/132b and 8b/10B encoding/decoding as per data rate.

- Capable of Manchester-II coding for Aux Transactions.

- Supports AUX-less ALPM Signaling.

- Option of bypass training is supported

- Supports ARVR SDP

- 8b/10b DP MST Mode Stream Symbol-to-MTP Mapping Rate Control Mandates

- SDP-only Transport without Main Video Stream 128b/132b

- No SDP or Main Video Stream 128b/132b

- SDP Error Detection in 128b/132b

- 128b/132b DP stream Symbol-to-MTP Mapping Rate Control Mandates

- Adaptive-Sync Operation for VESA AdaptiveSync

- Panel Replay Function

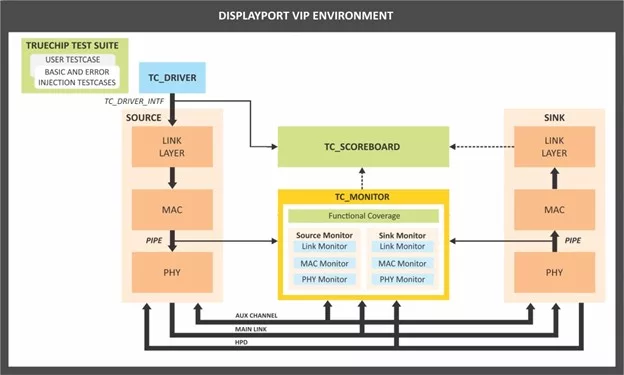

Block Diagram

Benefits

- Available in native System Verilog (UVM/OVM/ VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity examples for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solutions and easy integration in IP and SoC environment

What’s Included?

- DisplayPort 1.4a BFM's for:

- Source - Link Layer

- Source - MAC Layer

- Source - PHY Layer

- Sink - Link Layer

- Sink - MAC Layer

- Sink - PHY Layer

- Branching Devices

- LTTPR

- DisplayPort layered monitor & scoreboard

- Test Environment & Test Suite:

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- Compliance Test Suite

- User Test Suite

- Integration Guide, User Manual and Release Note

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about Displayport IP core

VESA Adaptive-Sync V2 Operation in DisplayPort VIP

Understanding LTTPR: Enabling High-Speed DisplayPort Interconnects in Complex System Designs

DisplayPort 2025: Navigating the Next Wave of Display Innovation

Audio Transport in DisplayPort VIP

DisplayPort 2.1 vs DisplayPort 1.4: A Detailed Comparison of Key Features

Frequently asked questions about DisplayPort IP cores

What is DisplayPort 2.1 Verification IP?

DisplayPort 2.1 Verification IP is a Displayport IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this Displayport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Displayport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.