USB 3.0 PHY, SMIC 40LL25 x1

The USB-C 3.0 and USB 3.0 PHY IP provide designers with the industry's best combination of low area and low power with support fo…

Overview

The USB-C 3.0 and USB 3.0 PHY IP provide designers with the industry's best combination of low area and low power with support for the leading process technologies from 65-nm to 14/16-nm FinFET. Both the USB-C and USB 3.0 PHYs offer a single efficient GDSII design that supports all four USB 3.0 speed modes (SuperSpeed, High-Speed, Full-Speed, and Low-Speed). To maximize battery life in mobile applications, the USB-C/USB 3.0 PHYs are designed to minimize power consumption and standby current. In addition, the USB-C 3.0 femtoPHY is optimized to support the USB Type-C connectivity specification.

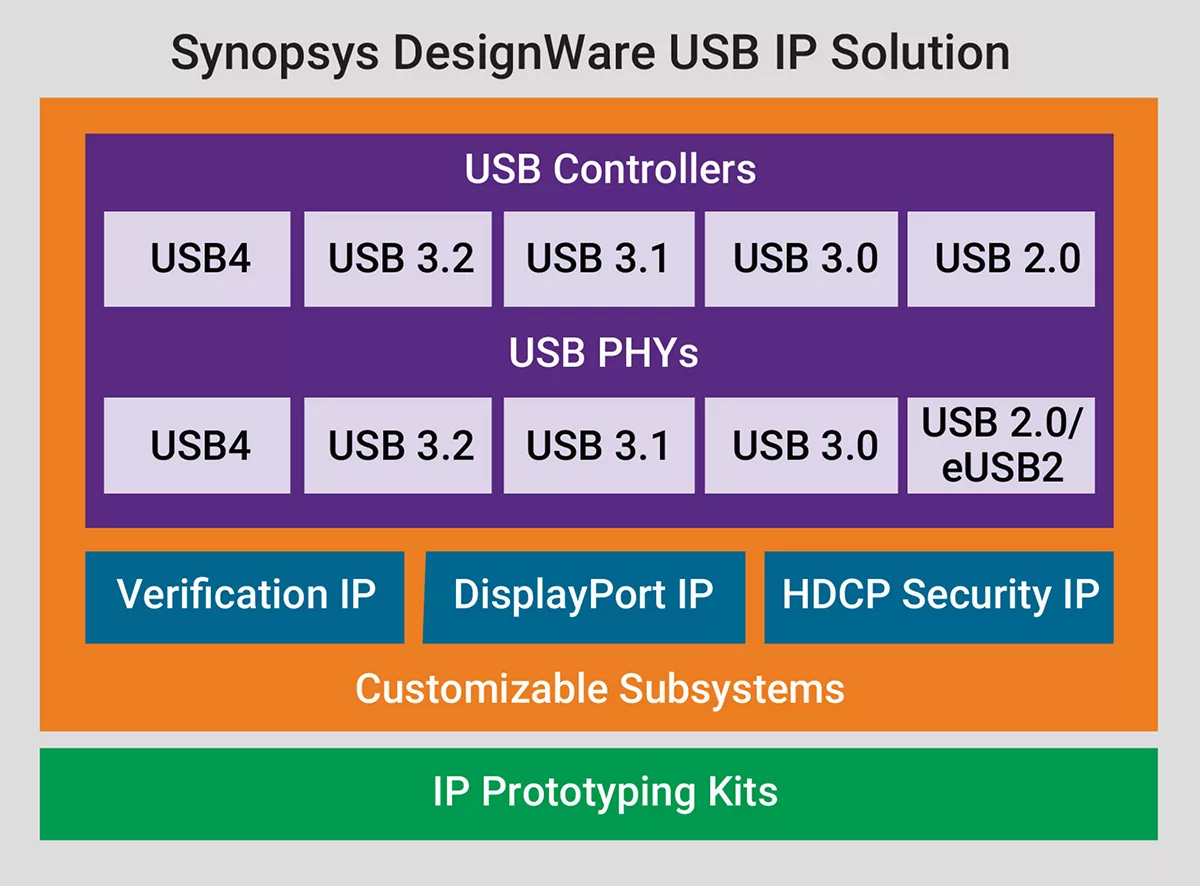

The USB IP is the most certified USB IP solution in the industry. With over 3,000 design wins and approximately three billion silicon-proven units shipped, the vendor complete USB IP solution, consisting of digital controllers, PHYs, verification IP, IP Prototyping Kits and IP software development kits, enables designers to lower integration risk and speed time-to-market.

Key features

- Part of a comprehensive IP solution including xHCI host and device controllers, PHYs, verification IP, IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C femtoPHY IP supports USB Type-C specification

- USB-C/USB 3.0 femtoPHY on 14/16-nm FinFET and 28-nm processes offers 50% smaller area use, high performance, and advanced power features

- Integrated PHY includes transmitter, receiver, PLL, digital core, and ESD

- Design minimizes area and power

- High yield: Designed to improve key operating margins by having less sensitivity to variations due to foundry process, chip and board parasitics, and process device variations

- The USB 3.0 PHY IP is USB-IF Certified

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| SMIC | 40nm | LL | — |

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is USB 3.0 PHY, SMIC 40LL25 x1?

USB 3.0 PHY, SMIC 40LL25 x1 is a Single-Protocol PHY IP core from Synopsys, Inc. listed on Semi IP Hub. It is listed with support for smic.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.