Timing Fragility Aware Selective Hardening of RISCV Soft Processors on SRAM Based FPGAs

This paper introduces a timing fragility aware selective hardening methodology for RISCV soft processors implemented on SRAM based FPGAs.

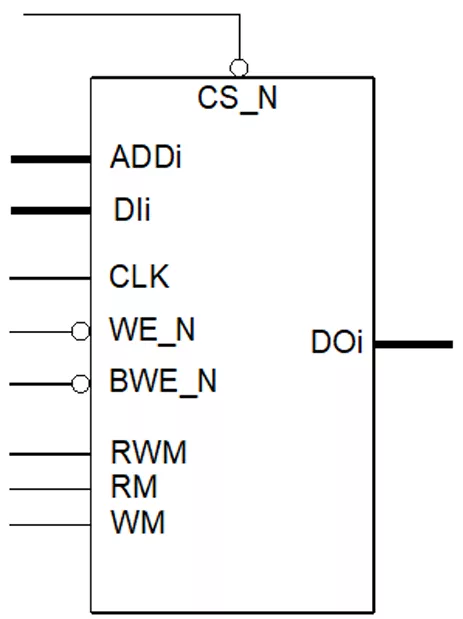

Single port SRAM compiler with low power retention mode.

Single port SRAM compiler with low power retention mode. Low leakage

| Bit Cell | Power Supply (V) |

| 6T | 0.9 |

Note: some files may require an NDA depending on provider policy.

Single Port Low Voltage SRAM Memory Compiler on N22ULL is a SRAM IP core from Nordic Semiconductor Seattle listed on Semi IP Hub.

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SRAM IP.

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.