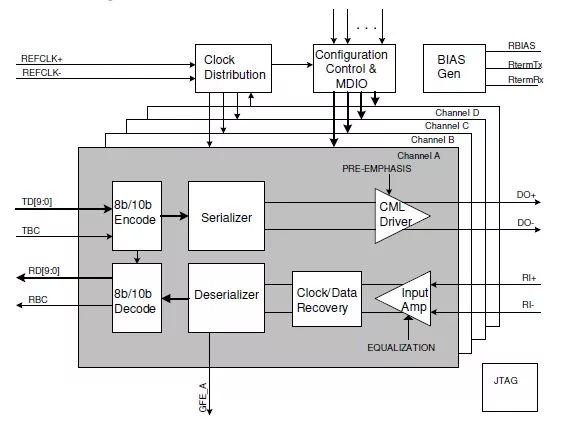

Quad 1.06/1.25/2.125/1.56/2.5/3.125 Gbps Backplane SerDes

TRC3104SBA is a Quad SerDes transceiver device, capable of transmitting 1.06 to 3.125Gb/s signals over Backplane, Fiber Channel, …

Overview

Key features

- Quad channel optimized for backplane , but can be used for FC and cable applications as well.

- Data rate 1 to 3.125Gb/s on high speed differential lines.

- Jitter tolerance of 0.72UIpp, and Jitter generation of 0.19UIpp.

- On chip 8bit/10bit encoder/decoder.

- selectable equalizer and pre-emphasis.

- Loopback abd BIST function (PRBS7 pattern).

- On chip JTAG and MDIO for test and setup.

- 256 pin PBGA package with 400mW per channel Pd.

Block Diagram

What’s Included?

- TRC3104SBA stand alone chip.

- TRC3104CBA core.

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 180nm | BCDG2 | — |

Specifications

Identity

Provider

Learn more about Multi-Protocol PHY IP core

How a 16Gbps Multi-link, Multi-protocol SerDes PHY Can Transform Datacenter Connectivity

16Gbps SerDes Multiprotocol Multilink PHY IP

32G Multi-Protocol SerDes PHY Out the Gate

New 16Gbps Multi-link, Multi-protocol SerDes PHY Enhances Datacenter Connectivity

One PHY, Zero Tradeoffs: Multi-Protocol PHY for Edge AI Interface Consolidation

Frequently asked questions about Multi-Protocol PHY IP cores

What is Quad 1.06/1.25/2.125/1.56/2.5/3.125 Gbps Backplane SerDes?

Quad 1.06/1.25/2.125/1.56/2.5/3.125 Gbps Backplane SerDes is a Multi-Protocol PHY IP core from TaraCom Integrated Products, Inc. listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this Multi-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Multi-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.