PCIe 6.0 (Gen6) Premium Controller with AMBA bridge

The configurable and scalable Controller IP for PCI Express® (PCIe®) 6.x supports all required features of the PCI Express 6.x sp…

Overview

The configurable and scalable Controller IP for PCI Express® (PCIe®) 6.x supports all required features of the PCI Express 6.x specifications, and can be configured by the user to support Endpoint (EP), Root Port, Dual Mode (DM), or Switch Port (SW) applications. The low-latency controller with new MultiStream architecture allows a full 64GT/s x16 lane bandwidth with support for up to 1024-bit data paths, while enabling timing closure at 1GHz. The controller can ensure optimal flow with multiple sources and in multivirtual channel implementations. Support for host, device, and dual mode enables early interoperability in absence of available 6.x hosts and interop partners. Designers can achieve maximum throughput for Arm-based SoCs with the controller’s support for the Arm AXI and for advanced host features including deferrable memory writes. The controller's reliability, availability and serviceability (RAS) features enhance data integrity, simplify firmware development and improve link bring-up.

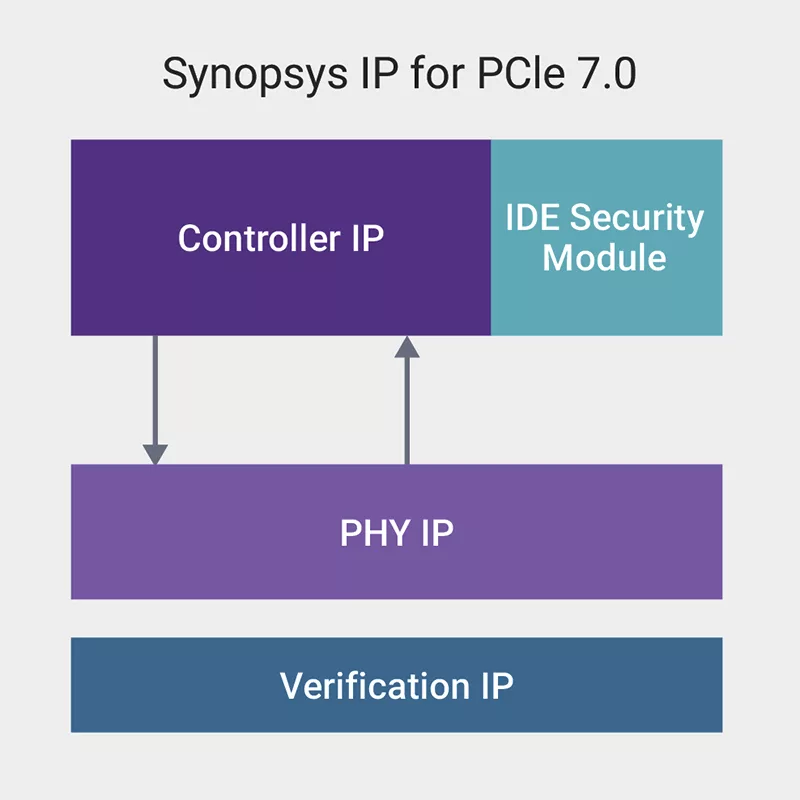

The Integrity and Data Encryption (IDE) Security Module for PCIe 6.x is pre-verified with the Controller IP to help designers protect data transfer in their SoCs against tampering and physical attacks. The standards-compliant IDE Security Modules are designed and validated with the Controller IP for PCIe to accelerate SoC integration, offering efficient confidentiality, integrity, and replay protection. The Secure PCIe Controllers with IDE provide support for the TEE Device Interface Security Protocol (TDISP), an Engineering Change Notice (ECN) released by PCI-SIG. TDISP standardized framework defines how to secure the interconnect between virtual machine hosts and devices, regardless of where the data center resides or who has access to the servers inside. The PCIe Controllers with IDE enable designers to build full TDISP support in their hyperscale SoCs and mitigate against data and system attacks to address the challenges of virtualized cloud security. Learn about the broad portfolio of Security Solutions for Interfaces.

The Controller IP for PCIe 6.x seamlessly interoperates with the silicon-proven PHY IP for PCIe 6 in advanced FinFET processes to provide a low-risk solution that designers can use to accelerate time-to-market and efficiently deliver differentiated products that require the 64GT/s PCIe 6.x technology.

Key features

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

- Supports the Synopsys native interface or the optional Arm® AMBA® 5/4/3 AXI application interface

- Configurable for low power, small area and low latency

- Enables efficient embedded DMA applications with Synopsys HyperDMA™

- Optional support for PCI Express Link Encryption via Integrity and Data Encryption (IDE) ECN

- Standards-compliant IDE Security Module protects data transfer for SoCs using the PCIe 6.x interface

- TDISP support for PCIe for Single-Root I/O Virtualization (SR IOV) and hardware security via IDE

Block Diagram

Specifications

Identity

Provider

Learn more about PCI Express IP core

How PCI Express Gives AI Accelerators a Super-Fast Jolt of Throughput

PCIe 6.0 - All you need to know about PCI Express Gen6

PCI Express 5 vs. 4: What's New? [Everything You Need to Know]

Complete Interface Solution for PCI Express 5.0 Launched

Doubling Bandwidth in Under Two Years: PCI Express Base Specification Revision 5.0, Version 0.9 is Now Available to Members

Frequently asked questions about PCIe IP cores

What is PCIe 6.0 (Gen6) Premium Controller with AMBA bridge?

PCIe 6.0 (Gen6) Premium Controller with AMBA bridge is a PCI Express IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this PCI Express?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PCI Express IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.