PCIe 3.0 (Gen3) Standard Controller EP/RP/DM/SW 32-128 bits

The configurable and scalable the Controller IP for PCI Express® (PCIe®) supports all required features of the PCI Express 5.0, 4…

Overview

The configurable and scalable the Controller IP for PCI Express® (PCIe®) supports all required features of the PCI Express 5.0, 4.0, 3.1, 2.1, 1.1 and PHY Interface for PCI Express (PIPE) specifications, and can be configured by the user to support Endpoint (EP), Root Port, Dual Mode (DM), or Switch Port (SW) applications. The high-quality, synthesizable IP portfolio is available in your choice of datapath widths, PIPE interface widths, operating frequencies, and over 1200 configuration parameters, all working together to enable designers to optimize their applications for size, power, latency and throughput. The Controller IP portfolio for PCI Express integrates quickly and easily into system-on-chip (SoC) designs with a user-friendly application interface or an industry-standard AMBA interface, and conservative timing suitable for a wide range of ASIC and FPGA technologies.

The Integrity and Data Encryption (IDE) Security Module for PCIe 5.0 is pre-verified with the Controller IP to help designers protect data transfer in their SoCs against tampering and physical attacks. The standards-compliant IDE Security Modules are designed and validated with the Controller IP for PCIe to accelerate SoC integration, offering efficient confidentiality, integrity, and replay protection. The Secure PCIe Controllers with IDE provide support for the TEE Device Interface Security Protocol (TDISP), an Engineering Change Notice (ECN) released by PCI-SIG. TDISP standardized framework defines how to secure the interconnect between virtual machine hosts and devices, regardless of where the data center resides or who has access to the servers inside. The PCIe Controllers with IDE enable designers to build full TDISP support in their hyperscale SoCs and mitigate against data and system attacks to address the challenges of virtualized cloud security. Learn about the broad portfolio of Security Solutions for Interfaces.

The Controller IP for PCI Express has been silicon validated in over 1800 designs with multiple hardware platforms, PHYs and PCIe verification suites, thereby reducing risk and improving time-to-market. As the industry standard for PCI Express, the vendor offers a comprehensive IP solution that is in volume production and has been successfully implemented in a wide range of applications.

Key features

- Supports all required features of the PCI Express 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s), 2.1 (5 GT/s), 1.1 (2.5 GT/s) and PIPE (8-, 16- and 32-bit) specifications

- Production-proven datapath support for 32b, 64b, 128b, 256b and 512b implementations

- Fully compliant with the PCI-SIG Single-Root I/O Virtualization (SRIOV) specification

- Application interfaces include the Synopsys native interface or the optional ARM® AMBA® 4 AXI and 3 AXI application interface (AMBA not available for Switch configurations)

- Synopsys Endpoint Controller interoperates with EpoStar’s NVMe controller and other high-performance NVMe implementations to provide a fast NVMe solution

- Silicon-proven, shipping in volume

- User-optimized configuration for low power, small area and low latency

- Standards-compliant Synopsys IDE Security Module protects data transfer for SoCs using the PCIe 5.0 or 4.0 interface

- TDISP support for PCIe for Single-Root I/O Virtualization (SR IOV) and hardware security via IDE

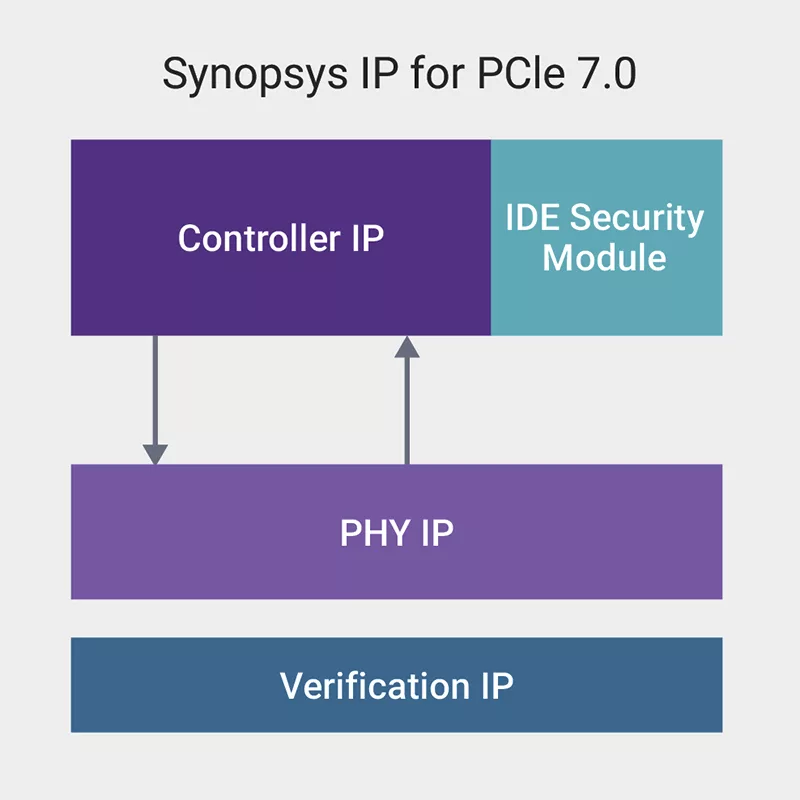

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about PCI Express IP core

How PCI Express Gives AI Accelerators a Super-Fast Jolt of Throughput

PCIe 6.0 - All you need to know about PCI Express Gen6

PCI Express 5 vs. 4: What's New? [Everything You Need to Know]

Complete Interface Solution for PCI Express 5.0 Launched

Doubling Bandwidth in Under Two Years: PCI Express Base Specification Revision 5.0, Version 0.9 is Now Available to Members

Frequently asked questions about PCIe IP cores

What is PCIe 3.0 (Gen3) Standard Controller EP/RP/DM/SW 32-128 bits?

PCIe 3.0 (Gen3) Standard Controller EP/RP/DM/SW 32-128 bits is a PCI Express IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this PCI Express?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PCI Express IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.