H.265 Encoder

The H.265 (HEVC – High Efficiency Video Coding) Encoder IP core enables efficient, high-quality video compression for application…

Overview

The H.265 (HEVC – High Efficiency Video Coding) Encoder IP core enables efficient, high-quality video compression for applications requiring low bandwidth and high-resolution output, such as broadcasting, video conferencing, surveillance, automotive, and cloud-based video services. It delivers real-time encoding of ultra-high-definition (UHD) content, significantly reducing storage and transmission demands while preserving visual fidelity.

The IP core supports Main, Main 10, and Main Still Picture profiles, offering full compliance with the H.265/HEVC standard. It features advanced rate control, low-latency encoding, support for multiple GOP structures, and compatibility with various chroma subsampling formats (4:2:0, 4:2:2, 4:4:4), making it well-suited for both professional and consumer-grade video applications.

Designed for flexibility, the IP core is highly configurable to meet specific design requirements, supporting both ASIC and FPGA implementations while optimizing for area, power, and performance.

Key features

- High-Efficiency Video Compression – Fully supports ITU-T H.265 | ISO/IEC 23008-2 HEVC standard, delivering up to 50% bandwidth savings over H.264

- Ultra-High Resolution and Frame Rate Support – Handles resolutions up to 16384×8640 at 120 fps, ideal for 4K/8K and high-frame-rate applications

- Flexible Coding Profiles and Bit Depth – Supports Main, Main10, and extended profiles up to Level 7.2 with 8-bit to 16-bit color depth support

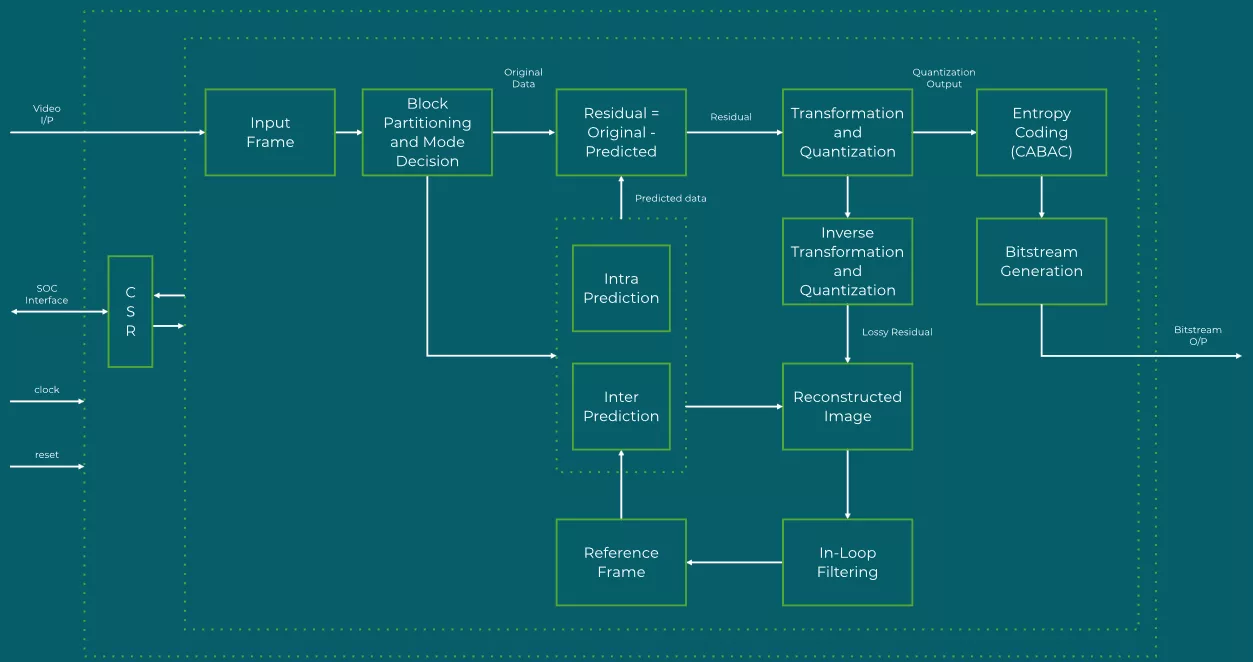

- Comprehensive Prediction and Transform Support – Implements all intra and inter prediction methods, 35 intra prediction modes, and quad-tree partitioning

- Advanced Filtering and Rate Control – Includes adaptive deblocking filter, sample adaptive offset (SAO), and support for both VBR and CBR encoding modes

- Optimized for System Integration – Offers standard AXI interfaces, programmable configuration, and support for 4:4:4, 4:2:2, 4:2:0, and monochrome formats

- Efficient Pipeline Architecture – Low-latency and high-throughput design with support for I, P, and B slices, transform skip, and CABAC entropy codingFull H.265/HEVC encoder functionality

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Video Processing IP core

Configurable Processors for Video Processing SOCs

FPGA-based video surveillance comes of age

Picking the right MPSoC-based video architecture: Part 1

Video encoding with low-cost FPGAs for multi-channel H.264 surveillance

Analysis: ARC's Configurable Video Subsystems

Frequently asked questions about Video Processing IP

What is H.265 Encoder?

H.265 Encoder is a Video Processing IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Video Processing?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Processing IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.