eUSB2V2 PHY

Proven solution featuring host and peripheral with industry- high performance, low power, and small area eUSB2V2 scales up to 4.8…

Overview

Proven solution featuring host and peripheral with industry-leading high performance, low power, and small area

eUSB2V2 scales up to 4.8Gbps of data rate with the flexibility to configure asymmetrical or symmetrical links to build an efficient system, depending on the intended application. In asymmetrical link mode, one direction can achieve speeds of up to 4.8Gbps, while the reverse can operate at a lower rate of 480Mbps. This flexibility allows for simpler designs, optimized power consumption, and reduced EMI noise. Symmetrical links can be configured to run at speeds between 960Mbps and 4.8Gbps.

Key features

- Up to 4.8Gbps scalable data rate

- Compliant to eUSB2V2 r1.0 / UTMI2.0 r0.9

- Configurable to Host or Peripheral

- Supports L1/L2 low power state

- Supports eUSB2V2 Compliance Modes and RxMargining Mode

- Support 19.2/24/48/100 MHz Ref Clocks

- APB interface for SoC register access and configuration

- Support for legacy protocol (HS Native Mode) operation

- Support pre and post-driver loopback test

- Supports eUSB2v1 HS Native Mode (480Mbps only)

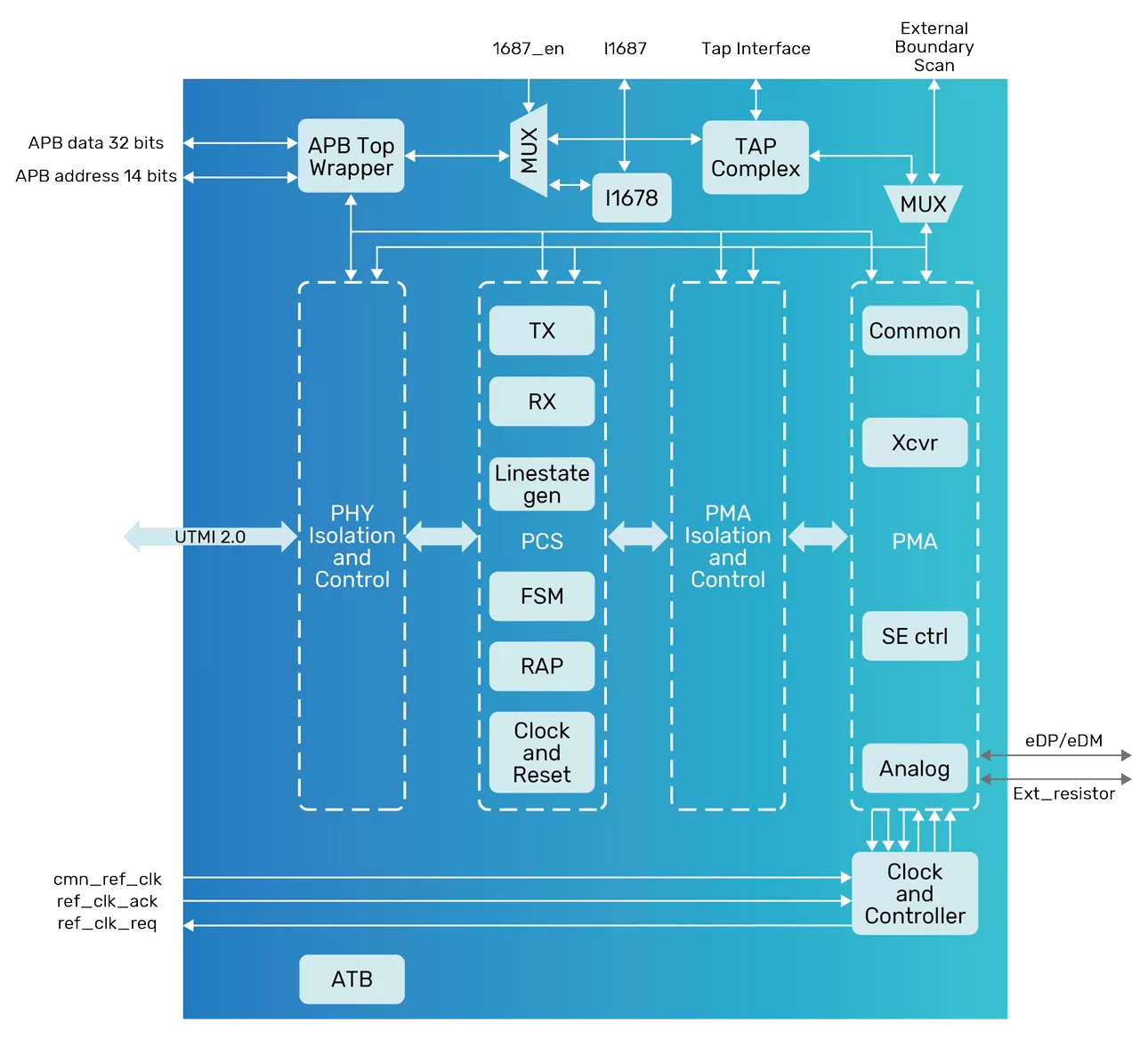

Block Diagram

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is eUSB2V2 PHY?

eUSB2V2 PHY is a Single-Protocol PHY IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.