DP and eDP TX/RX PHY IP

The DP and eDP TX/RX PHY IP provides a compact, low-power solution for high-speed external display interfaces.

Overview

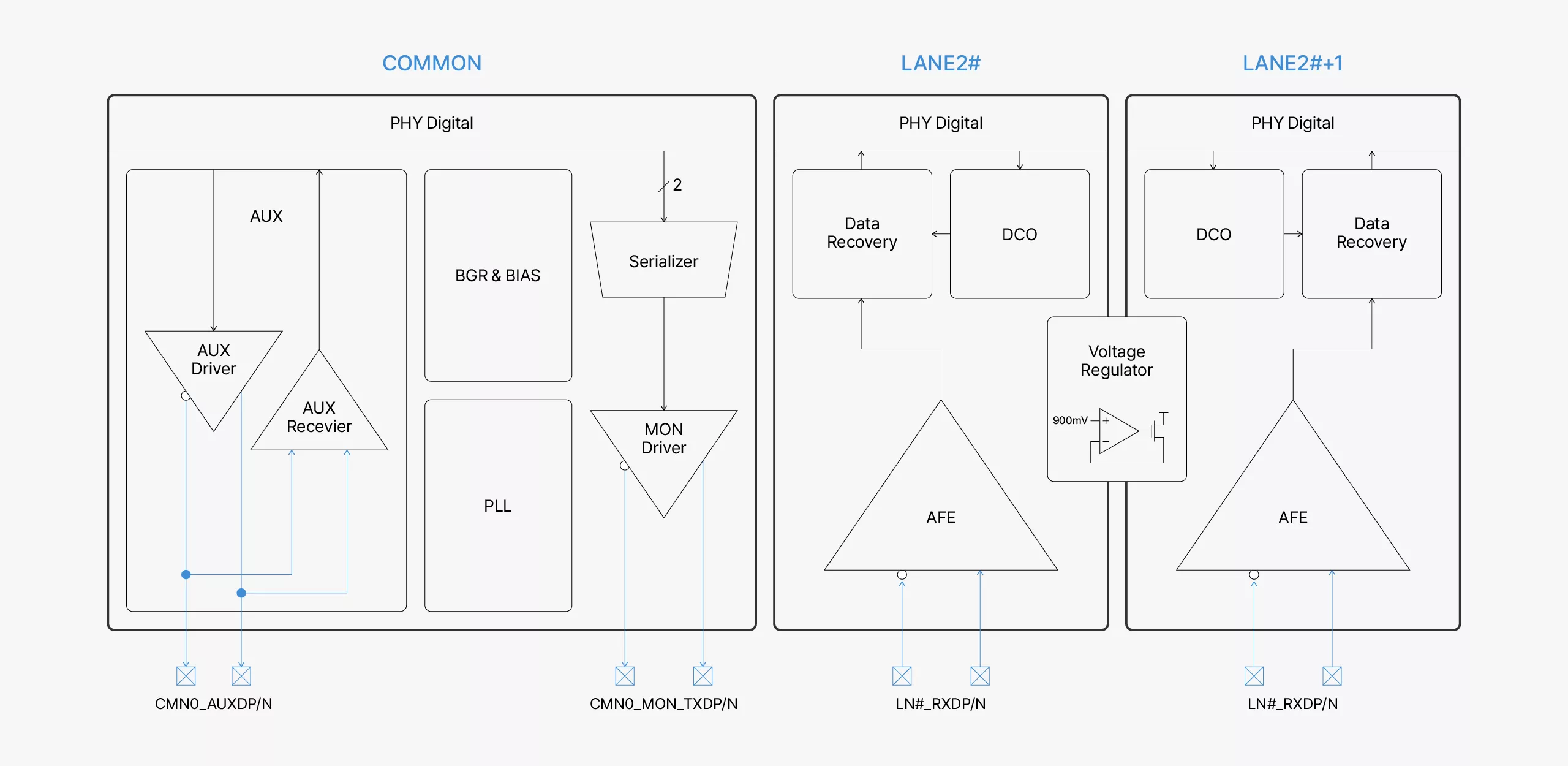

The DP and eDP TX/RX PHY IP provides a compact, low-power solution for high-speed external display interfaces. It supports various lane configurations, bidirectional data flow in both NS and EW directions, and is optimized for area efficiency on advanced FinFET nodes.

The IP includes built-in self-test features such as loopback mode and PRBS pattern checking, ensuring reliable performance and simplified validation in DisplayPort and Embedded DisplayPort applications.

Key features

- eDP v1.5 compliant

- Supports for 1.62Gbps to Max 8.1Gbps data rate

- PSR, PSR2 supported for low power consumption ( FW_SLEEP, FW_STANDBY supported )

- Supports for eDP v1.5 feature such as AUX-less Link Training

- Adaptive continuous time linear equalizer (CTLE) and decision feedback equalization (DFE)

- Automatic calibration of analog circuits and offset correction

- Built-in eye open monitor

- Built-in self-test (BIST) including PRBS7 and eDP Compliant TPS1 to TPS4 generation and checker

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is DP and eDP TX/RX PHY IP?

DP and eDP TX/RX PHY IP is a Single-Protocol PHY IP core from Qualitas Semiconductor listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.