4.25 Gbps Multi-Standard SerDes

The MXL4254A is a silicon proven Quad Gigabit SerDes implemented in digital CMOS technology.

Overview

The MXL4254A is a silicon proven Quad Gigabit SerDes implemented in digital CMOS technology. Each of the four channels supports data rate up to 4.25 Gbps.

It is compatible with router-backplane links, PCI Express, SATA, RapidIO, 10 Gbps Ethernet (XAUI), FibreChannel, SFI-5, SPI-5, and other communication applications.

Key features

- 1.0 to 4.25 Gbps operation per channel

- 1.2V power supply, CMOS design

- Low power dissipation

- Minimal external components

- Programmable voltage output swing at high-speed serial output

- Programmable integrated termination resistors in transmitter and receiver.

- Programmable Tx pre-emphasis and Rx post-equalization

- Local and remote serial loop-back capability

- Modular design to facilitate customization and process migration

- Can be easily integrated into multiple Quads

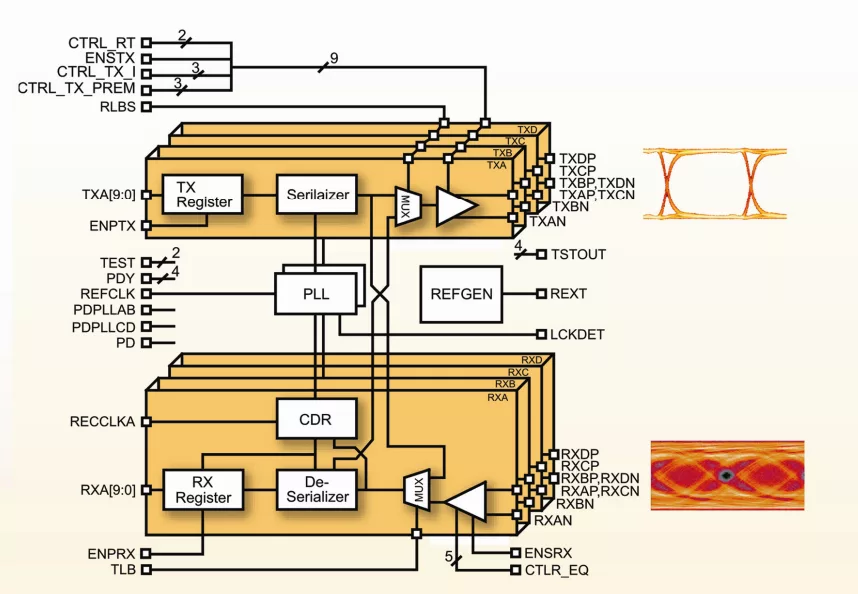

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Multi-Protocol PHY IP core

How a 16Gbps Multi-link, Multi-protocol SerDes PHY Can Transform Datacenter Connectivity

16Gbps SerDes Multiprotocol Multilink PHY IP

32G Multi-Protocol SerDes PHY Out the Gate

New 16Gbps Multi-link, Multi-protocol SerDes PHY Enhances Datacenter Connectivity

One PHY, Zero Tradeoffs: Multi-Protocol PHY for Edge AI Interface Consolidation

Frequently asked questions about Multi-Protocol PHY IP cores

What is 4.25 Gbps Multi-Standard SerDes?

4.25 Gbps Multi-Standard SerDes is a Multi-Protocol PHY IP core from Mixel, Inc. listed on Semi IP Hub.

How should engineers evaluate this Multi-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Multi-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.