32G PHY, TSMC N5 x1, North/South (vertical) poly orientation

The multi-lane Multi-Protocol 32G PHY IP is part of a high-performance multi-rate transceiver portfolio for high-end networking a…

Overview

The multi-lane Multi-Protocol 32G PHY IP is part of a high-performance multi-rate transceiver portfolio for high-end networking and cloud computing applications. The PHY is small in area and provides a low active and standby power solution that supports multiple electrical standards, including PCI Express (PCIe) 5.0, 1G to 400G Ethernet, Cache Coherent Interconnect for Accelerators (CCIX), Compute Express Link (CXL), SATA, and other industry-standard interconnect protocols Using leading-edge design, analysis, simulation, and measurement techniques, the multi-protocol 32G PHY delivers signal integrity and jitter performance that exceeds the standards electrical specifications.

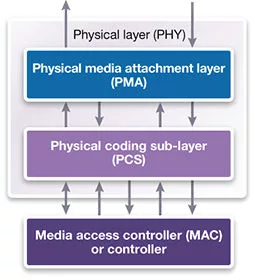

The configurable transmitter and receiver equalizers along with Continuous Calibration and Adaptation (CCA) enable designers to control and optimize signal integrity and performance across voltage and temperature variations. The PHY provides advanced power management features for both standby and active power. The BERT and internal eye monitor provide on-chip testability and visibility into channel performance. The PHY integrates seamlessly with the Synopsys Physical Coding Sublayer (PCS) and Media Access Control (MAC) to reduce design time and to help designers achieve first-pass silicon success.

Key features

- Supports 1.25 to 32 Gbps data-rate

- Supports PCI Express 5.0, 1G to 400G Ethernet, CCIX, CXL, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC)

- PCIe Separate Refclk Independent SSC (SRIS) and power management features

- Ethernet Electrical Energy Efficient (EEE)

- Reference clock sharing for aggregated macro configurations

- Continuous time linear equalizer (CTLE), decision feedback equalization (DFE) and feed forward equalization (FFE)

- Embedded bit error rate tester (BERT) and internal eye monitor

- Supports IEEE 1149.6 AC Boundary Scan

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Multi-Protocol PHY IP core

How a 16Gbps Multi-link, Multi-protocol SerDes PHY Can Transform Datacenter Connectivity

16Gbps SerDes Multiprotocol Multilink PHY IP

32G Multi-Protocol SerDes PHY Out the Gate

New 16Gbps Multi-link, Multi-protocol SerDes PHY Enhances Datacenter Connectivity

One PHY, Zero Tradeoffs: Multi-Protocol PHY for Edge AI Interface Consolidation

Frequently asked questions about Multi-Protocol PHY IP cores

What is 32G PHY, TSMC N5 x1, North/South (vertical) poly orientation?

32G PHY, TSMC N5 x1, North/South (vertical) poly orientation is a Multi-Protocol PHY IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this Multi-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Multi-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.