PCIe Gen4.0 PHY IP

The PCIe Gen4.0 PHY IP offers a low-power, compact solution with proven performance and robust signal and power integrity, making…

Overview

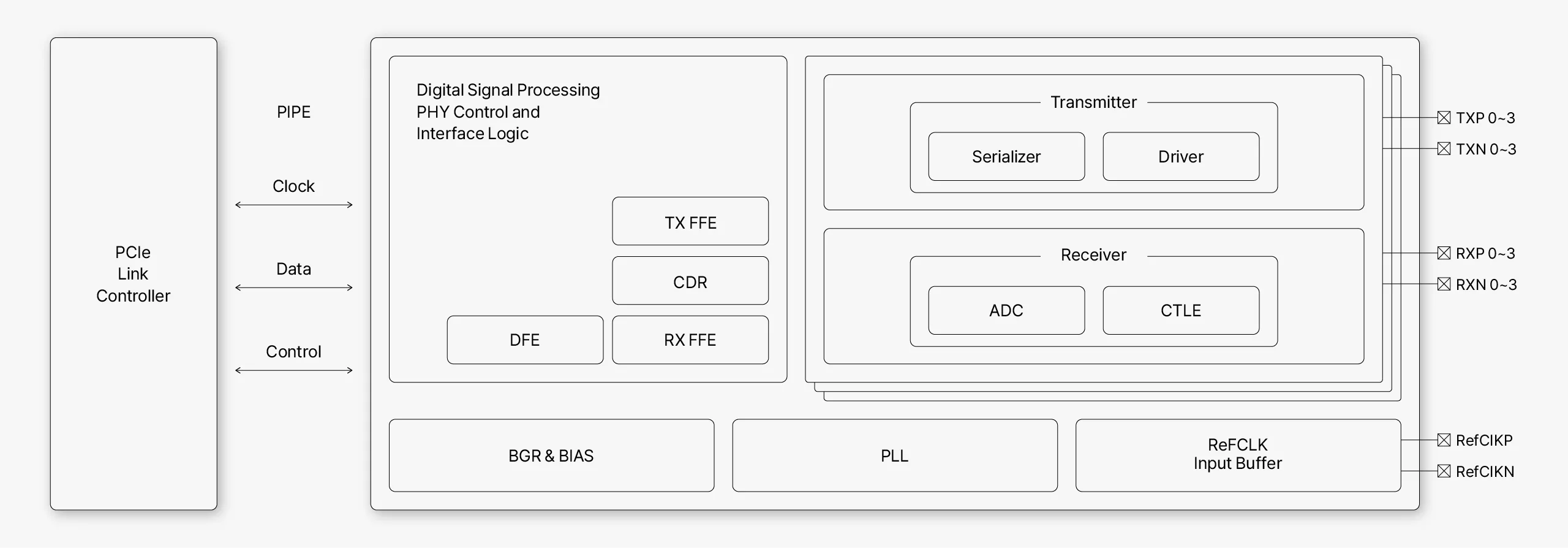

The PCIe Gen4.0 PHY IP offers a low-power, compact solution with proven performance and robust signal and power integrity, making it suitable for a wide range of high-speed interface environments. Optimized for seamless integration with controller IPs, it enhances design efficiency and reliability. Built-in self-test (BIST), loopback, and scan test features significantly improve debug capability, while optional delivery as a complete PCIe 4.0 subsystem meets diverse customer needs. This robust IP has been successfully deployed in mass-production for applications including data centers, automotive systems, and surveillance devices.

Key features

- Best-in-class Power / Performance / Area competitiveness

- Compliant to PCIe 4.0 Base specification

- Supports lane configurations according to the user’s demands

- Supports data rates of 2.5GT/s, 5.0GT/s, 8.0GT/s and 16GT/s

- Including PCS supported in soft-macro form

- Supports power-down modes of P0, P1, P2, P1.ss and P1.cpm

- Supports fully adaptive channel equalization

- Built-in self-test feature producing and checking PRBS pattern

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Multi-Protocol PHY IP core

How a 16Gbps Multi-link, Multi-protocol SerDes PHY Can Transform Datacenter Connectivity

16Gbps SerDes Multiprotocol Multilink PHY IP

32G Multi-Protocol SerDes PHY Out the Gate

New 16Gbps Multi-link, Multi-protocol SerDes PHY Enhances Datacenter Connectivity

One PHY, Zero Tradeoffs: Multi-Protocol PHY for Edge AI Interface Consolidation

Frequently asked questions about Multi-Protocol PHY IP cores

What is PCIe Gen4.0 PHY IP?

PCIe Gen4.0 PHY IP is a Multi-Protocol PHY IP core from Qualitas Semiconductor listed on Semi IP Hub.

How should engineers evaluate this Multi-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Multi-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.