1.8V Capable GPIO on Samsung Foundry 4nm FinFET

The 1.8V capable GPIO is an IP macro for on-chip integration.

Overview

The 1.8V capable GPIO is an IP macro for on-chip integration. It is a 1.8V general purpose I/O built with a stack of 1.2V MOS FINFET devices. It is controlled by 0.75V (core) signals.

Supported features include core isolation, output enable and pull enable. Extra features such as input enable/disable, programmable drive strength and pull select, can be supported upon request.

By default, a 2kV HBM ESD protection is included. This is however easily scaled to any desired level. This specific IP macro is designed in Samsung 4nm FINFET, and can be ported to other technologies upon request using Sofics inhouse design tool flow.

Key features

- Overvoltage tolerant design

- Deep N-Well

- Core domain isolation

- Vertical orientation

- Temp range -40°C to 125°C TJ

- 50kΩ pullup/pulldown

- Integrated 2kV HBM ESD

- 5A of CDM current

- 0.75V digital interface at the core side

- Bias generation circuit can be shared over multiple I/O instances

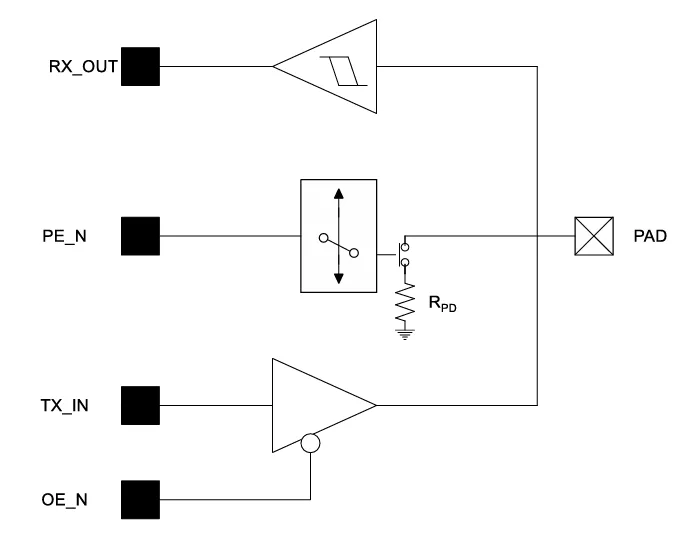

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| Samsung | 4nm | SF4 | — |

Specifications

Identity

Provider

Learn more about GPIO IP core

A Generic Solution to GPIO verification

Integrating Post-Quantum Cryptography (PQC) on Arty-Z7

ESD Protection for an High Voltage Tolerant Driver Circuit in 4nm FinFET Technology

From I2C to I3C: Evolution of Two-Wire Communication in Embedded Systems

One Platform, Five Libraries: Certus Semiconductor’s I/O IP Portfolio for Every Application on TSMC 22nm ULL/ULP Technologies

Frequently asked questions about GPIO Pad Library IP cores

What is 1.8V Capable GPIO on Samsung Foundry 4nm FinFET?

1.8V Capable GPIO on Samsung Foundry 4nm FinFET is a GPIO IP core from Sofics listed on Semi IP Hub. It is listed with support for samsung.

How should engineers evaluate this GPIO?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this GPIO IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.