1.8V/3.3V GPIO With I2C Compliant ODIO in GF 55nm

GPIO, ODIO and Analog I/Os with Robust ESD Protection in GF 55nm This I/O Library, developed on GlobalFoundries 55nm CMOS, delive…

Overview

GPIO, ODIO and Analog I/Os with Robust ESD Protection in GF 55nm

This I/O Library, developed on GlobalFoundries 55nm CMOS, delivers a complete suite of digital and analog I/O solutions with robust 2 kV HBM / 500 V CDM ESD protection and latch-up immunity. The library includes 1.8/3.3 V GPIOs supporting GMII and LVCMOS standards, I2C-compliant ODIOs, and flexible analog I/Os (ANA/DANA) with integrated ESD. Complemented by a full set of power, filler, corner, and transition cells, the VZ55 library enables reliable padring construction across mixed-signal designs. With wide voltage support, industrial temperature range (-40°C to 125°C), and cross-domain ESD protection, VZ55 provides a scalable, production-ready I/O platform for advanced SoC integration.

Library Summary

| Item | Description |

| Core VDD | 1.2V |

| VDDIO | 1.8V-3.3V |

| Temp-40C to 125C | Max Load SeeGPIO/ODIOSpec |

| ESD | 2kV HBM/ 500V CDM |

| BEOL | 1P6M |

| Pad Size | 45um x 39um |

| Cell Heights | 80um |

| Cell Pitch | 60um |

Key features

Analog I/O Features

- ANA: 1.8V/3.3V analog I/O for analog pad banks

- DANA: 3.3V analog I/O for digital pad banks

- Direct bondpad or core-side analog pin access

- PrimaryandsecondaryESDprotectiondiodesintegrated

- DGANAtransition cells provide safe cross-domain ESD protection

GPIO Features

- 1.8V-3.3V GPIO

- Supports up to 200MHz operation across all voltages

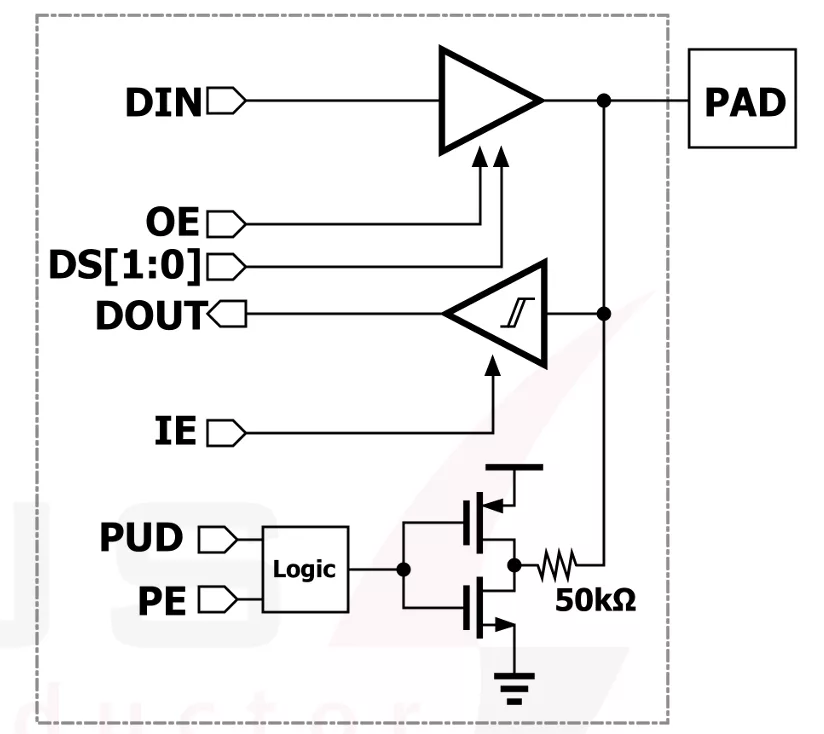

- Multiple drive strengths (configurable via DS0/DS1)

- Built-in 50k pull-up/pull-down termination option

- Standards compliant: GMII and LVCMOS

ODIO Features

- 1.8V-3.3V ODIO with I2C and GMII compatiblity

- Optimized for I2C Standard, Fast, and Fast-Mode Plus (1 MHz)

- Glitch filter (50 ns) ensures robust bus noise rejection

- Strong low-side drive capability for capacitive bus loading

- GMII thresholds supported for networking/bus application ( 125MHz class)

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| GlobalFoundries | 55nm | 55 550 nm | — |

Specifications

Identity

Provider

Learn more about GPIO IP core

A Generic Solution to GPIO verification

Integrating Post-Quantum Cryptography (PQC) on Arty-Z7

ESD Protection for an High Voltage Tolerant Driver Circuit in 4nm FinFET Technology

From I2C to I3C: Evolution of Two-Wire Communication in Embedded Systems

One Platform, Five Libraries: Certus Semiconductor’s I/O IP Portfolio for Every Application on TSMC 22nm ULL/ULP Technologies

Frequently asked questions about GPIO Pad Library IP cores

What is 1.8V/3.3V GPIO With I2C Compliant ODIO in GF 55nm?

1.8V/3.3V GPIO With I2C Compliant ODIO in GF 55nm is a GPIO IP core from Certus Semiconductor listed on Semi IP Hub. It is listed with support for globalfoundries.

How should engineers evaluate this GPIO?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this GPIO IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.