Flipchip 1.8V/3.3V I/O Library with ESD-hardened GPIOs in TSMC 12nm FFC/FFC+

A 1.8V/3.3V flip-chip I/O library with ESD-immune GPIOs and integrated POC circuitry in TSMC FFC/FFC+.

Overview

A 1.8V/3.3V flip-chip I/O library with ESD-immune GPIOs and integrated POC circuitry in TSMC FFC/FFC+.

This library is a production-ready I/O library built on the TSMC 12nm process. The library features 1.8V to 3.3V GPIOs with programmable drive strength, hysteresis, and control logic. It includes support cells for all power domains: 0.8V, 1.8V, and I/Oand incorporates latch-up immune, JEDEC-compliant ESD structures. The library is designed for flip-chip packaging and includes vertical and horizontal variants to support all die edge orientations. All power domains include integrated power-on control (POC) cells for safe and reliable sequencing.

Operating Conditions

| Parameter | Value |

| VDDIO | 1.8V / 3.3V +/-10% |

| Core VDD | 0.8V +/-10% |

| Tj | -40°C to 125°C |

Cell Size and Metal Stack

| Cell Size | Metal Stack |

| MH_IO | 25um x 53um |

| MH_VDDIO_POC | 50um x 53um |

| Metal Stack | 1P9M |

Library Cell Summary

| Cell Type | Feature |

| MH_IO | 1.8V/3.3V GPIO, 2-bit drive strength |

| MH_VDDIO_ | POC POC and ESD protection |

| MH_VDD / VDD18 | 0.8V / 1.8V power cells w/ ESD |

| MH_CORNER | Power continuity at pad corner |

Key features

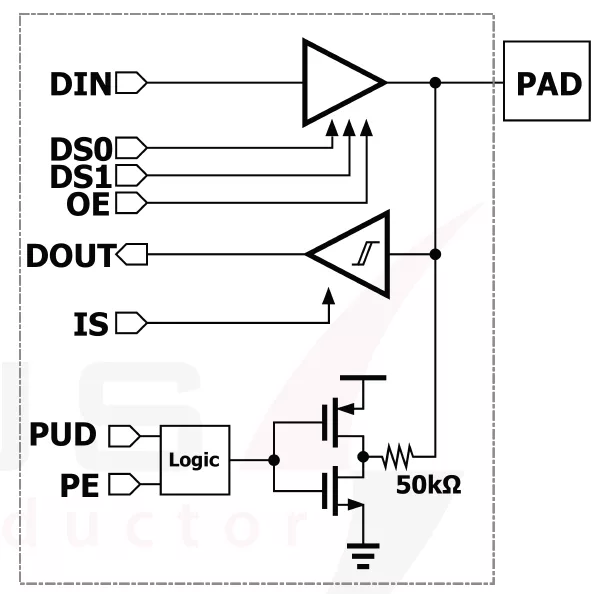

GPIO Features

- Dual drive strength control (DS0/DS1)

- Output enable, input hysteresis, pull-up/down control

- Fully ESD compliant with local clamp topology

Power and POC Features

- Dedicated VDDIO, VDD18, and VDD core power pads

- Integrated POC signals for safe sequencing

- Required for robust ESD paths across pad ring

Compliance

- 2kV HBM per JEDEC JS-001

- 500V CDM

- Latch-up immune

- Flip-chip compatible

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 12nm | FFC+ | — |

Specifications

Identity

Provider

Learn more about GPIO IP core

A Generic Solution to GPIO verification

Integrating Post-Quantum Cryptography (PQC) on Arty-Z7

ESD Protection for an High Voltage Tolerant Driver Circuit in 4nm FinFET Technology

From I2C to I3C: Evolution of Two-Wire Communication in Embedded Systems

One Platform, Five Libraries: Certus Semiconductor’s I/O IP Portfolio for Every Application on TSMC 22nm ULL/ULP Technologies

Frequently asked questions about GPIO Pad Library IP cores

What is Flipchip 1.8V/3.3V I/O Library with ESD-hardened GPIOs in TSMC 12nm FFC/FFC+?

Flipchip 1.8V/3.3V I/O Library with ESD-hardened GPIOs in TSMC 12nm FFC/FFC+ is a GPIO IP core from Certus Semiconductor listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this GPIO?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this GPIO IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.