Very high performance IEEE-754 modules

The A2FM product is a collection of floating-point execution units compliant with the ANSI/IEEE Std 754-1985, IEEE Standard for B…

Overview

The A2FM product is a collection of floating-point execution units compliant with the ANSI/IEEE Std 754-1985, IEEE Standard for Binary Floating-Point Arithmetic (IEEE-754 Standard). The units are designed for high frequency, high throughput implementations. Each unit is implemented as a state less pipeline that can easily be integrated into a high-performance processor design.

Each unit is targeted for a clock cycle with only 10-12 gate delays (excluding setup and clock skew). The add and multiply units implement 5-cycle pipelines. The conversion unit implements a 2-cycle pipeline, and the compare unit a 1-cycle pipeline. All units can sustain a 1-cycle throughput. The multiply unit supports fused floating-point multiply add, as well as a variety of 32-bit integer multiply functions.

IEEE-754 Compliance

The A2FM modules are designed to provide a powerful floating-point capability while minimizing die size cost. To minimize unnecessary design size, some of the rarely used features of the IEEE specification are not implemented directly in the hardware design. The following IEEE-defined operations are not directly supported in A2FM hardware, but can be supported with software support:

- Gradual Underflow

- Denormal Numbers

In place of gradual underflow, the A2FM modules implement a flush-to-zero approach when underflow occurs. This feature allows the A2FM modules to maintain a one-cycle throughput in all operand cases, and minimizes design size.

Key features

- IEEE-754 compliant (except underflow)

- Flush to zero underflow implementation

- Single precision

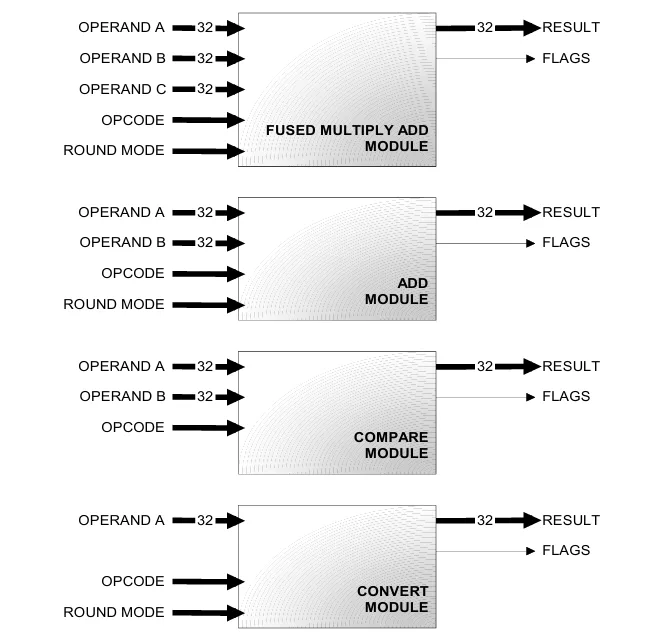

- Fused Multiply Add Module (5 STAGE PIPE)

- Floating Point Multiply

- Floating Point Amultiply-Add

- 32-bit integer signed/unsigned

- 32-bit integer signed round & shift

- 32-bit integer signed and shift

- 32-bit integer signed absolute result

- Add Module (5 STAGE PIPE)

- Floating Point Add / Subtract

- All IEEE rounding modes supported

- All IEEE exception flags supported

- Compare Unit (1 STAGE PIPE)

- Floating Point Compare

- Floating Point min/max/saturate

- Floating-point NAN test

- Floating-point Absolute Value

- Conversion Module (2 STAGE PIPE)

- Convert floating-point to/from integer

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about FPU IP core

A formal-based approach for efficient RISC-V processor verification

Efficient Verification of RISC-V processors

Formally Verifying Processor Security

JasperGold: the Next Generation

NXP Introduces Tensilica HiFi 4 DSP-based Platforms to Secure IoT Edge Devices

Frequently asked questions about FPU IP cores

What is Very high performance IEEE-754 modules?

Very high performance IEEE-754 modules is a FPU IP core from Advanced Architectures listed on Semi IP Hub.

How should engineers evaluate this FPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this FPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.