Can Your NPU Run DOOM? Chimera Can.

Is your NPU DOOMed? Quadric's Chimera GPNPU runs every AI model — and a complete DOOM engine. Find out why Quadric is different.

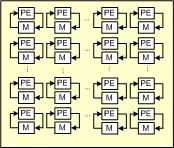

This circuit uses Altera’s new Arria and Stratix 10 FPGAs with hardwired support for floating-point operations (IEEE754).

Note: some files may require an NDA depending on provider policy.

Floating-point (IEEE 754) IP based on Arria 10 and Stratix 10 FPGAs is a FPU IP core from Centar listed on Semi IP Hub.

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this FPU IP.

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.