USB 10Gbps Device Controller

Leveraging the benefits of USB 3.2 Gen 1 device controller, USB 3.2 Gen 2 is designed using the FPGA built-in transceiver.

Overview

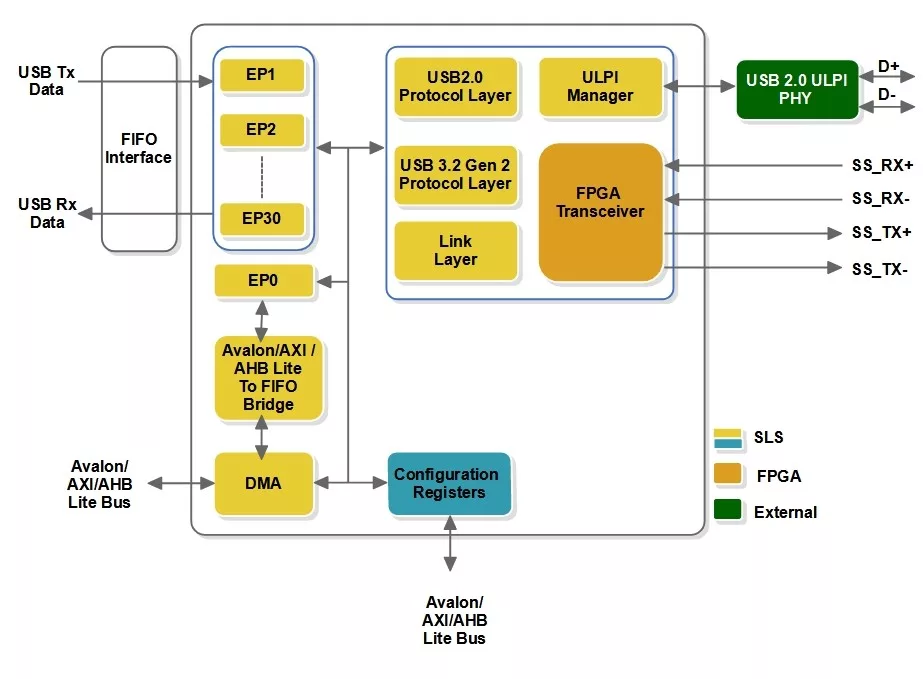

Leveraging the benefits of USB 3.2 Gen 1 device controller, USB 3.2 Gen 2 is designed using the FPGA built-in transceiver. It is a one-stop solution for all USB requirements ranging from USB 3.2 to USB 2.0. It supports SuperSpeed+ (SSP), SuperSpeed (SS), High Speed (HS) and Full Speed (FS) communication modes. The Core architecture allows to use minimal pins from FPGA for USB 3.2 interface with better stability. It provides USB 2.0 backward compatibility using an external USB 2.0 ULPI PHY.

It has been designed to provide simplicity and flexibility along with highest throughput i.e. >8.5Gbps. Avalon/AXI/AHB Lite interface allows to manage the control transfer using software, provides flexibility, while FIFO interface allows to transfer the data over non-control endpoint ensuring highest throughput.

FPGA Supported:

| FPGA | Supported Device Family |

| Intel |

Agilex 7, Cyclone 10, Arria 10, Stratix 10, Cyclone V1, Arria V1, Stratix V1 |

| Microchip | PolarFire, PolarFire SoC |

| Lattice Semiconductor | CrossLink-NX1, Certus Pro NX1 |

Note:

- Supports up to Gen1 mode.

Key features

- USB 3.2 Specific Features

- Supports SuperSpeedPlus (SSP - USB 3.2 Gen 2) mode and ports SuperSpeed (SS - USB 3.2 Gen 1) mode

- Uses FPGA Transceiver as a PHY layer and thus eliminates need for external PHY for USB 3.2

- USB 2.0 Specific Features

- Supports High Speed (HS) and Full Speed (FS) modes

- Provides well-known ULPI interface to interact with external USB 2.0 PHY

- Ease of Use

- Ready to use component

- Simple FIFO interface to transfer data over non-control endpoint

- Flexibility

- Capable to support up to 31 endpoints (1 default control endpoint, 15 IN endpoints and 15 OUT endpoints)

- Allows to select number of buffers per endpoint based on the requirement

Block Diagram

Benefits

- No need for external PHY for USB 3.1 Gen 1 and Gen 2 interface

- Uses in-built transceiver as PHY layer

- Requires less pins compared to external PHY

Applications

- Imaging Device

- Storage Devices

- Machine Vision

- Data Centers

Specifications

Identity

Video

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Frequently asked questions about USB IP cores

What is USB 10Gbps Device Controller?

USB 10Gbps Device Controller is a USB IP core from System Level Solutions, Inc. listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.