USB 2.0 VMM System Verilog VIP

The USB 2.0 VMM SystemVerilog VIP is fully documented, off the shelf component for the verification of the USB 2.0 compliant Func…

Overview

The USB 2.0 VMM SystemVerilog VIP is fully documented, off the shelf component for the verification of the USB 2.0 compliant Function Controller.

USB 2.0 VMM VIP is developed using the Synopsys VMM methodology that is used in dynamic simulation of USB 2.0 based design. Verification IP created according to the VMM methodology allows for easy "plug-and-play" use in VMM test benches.

The USB2.0 VIP uses SystemVerilog to create comprehensive verification environments using coveragedriven, constrained-random and assertion-based techniques. This VIP can work in a standalone mode i.e. can be plugged with any Function Controller with standard pinouts without disturbing the structure.

The VIP provides a fast and accurate way to simplify and speed-up the Device verification task. In a complex design process, verification may take up to 70% of the development time. USB 2.0 VMM SV VIP speeds up the verification process providing a compelling cost and time to market.

The USB 2.0 function controller is a highly integrated solution for USB applications and provides 480 Mb/s high speed USB interface. It is a single core solution incorporating USB 2.0 protocol operating in Link Layer of Open System Interconnect (OSI) which significantly reduces the time and cost of implementing complex USB 2.0 target system designs.

Product Specifications

- The VIP can work with either 8-bit or 16-bit standard USB 2.0 Devices

- Error Injection Mechanism, which can be turned ON or OFF for a given simulation run incorporates around 45+ scenarios for different Error types

- Provides a choice of resetting the DUT to either High-Speed or Full-Speed Mode upon startup

- Supports RESET / SUSPEND / RESUME operation, as well as on-the-fly Reset switch- over from High-Speed to Full-Speed or vice-versa

Key features

- Synopsys VMM complaint.

- Absence of inter-module dependencies makes the VIP highly reusable.

- Hierarchical Seed Randomization.

- Fully Constrained Driven Randomization of Packets achieved by Randomization of various fields of the Packet.

- Intelligent and versatile Scoreboard that provides:

- A bird′s eye view of the USB Transactions

- Total number of Transactions

- Statistics of Transfer Types

- Count of Token, Data and Handshake Packets sent / received.

- Statistics on RESET / SUSPEND / RESUME activities

- Error Injection statistics

- Overall count of good / bad Packets.

- The following USB 2.0 Modes are supported:

- Full-Speed / High-Speed 8-bit

- Full-Speed / High-Speed 16-bit

- Low-Speed Only

- Full-Speed Only

- Programmable and Randomized Transfer Types, namely INTERRUPT, ISOCHRONOUS, BULK and CONTROL

- Provides a choice for inhibiting SUSPEND and / or RESET operation through use of simple macros.

- Auto Programming – cum selection of Clocks for different Modes – 6 MHz (Low-Speed Only Mode), 30 MHz (16-bit High-Speed / Full-Speed Mode), 48 MHz (Full-Speed Only Mode) or 60 MHz (8-bit High-Speed / Full- Speed Mode)

- Supports up to 16 Endpoints as per the USB 2.0 Standard. Endpoints can be either IN, OUT or NOT_IMPLEMENTED through userdefined header declarations, with Endpoint0 as INOUT

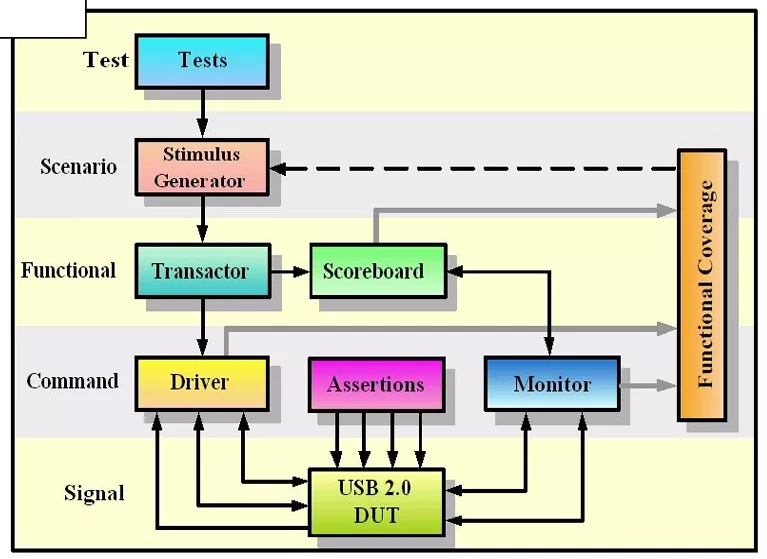

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Frequently asked questions about USB IP cores

What is USB 2.0 VMM System Verilog VIP?

USB 2.0 VMM System Verilog VIP is a USB IP core from Silicon Cores - a Div. of Silicon Interfaces listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.