Vendor:

T2M GmbH

Category:

USB

USB 2.0 OTG High / Full / Low- Speed Dual Role IP Core

Our company offers a configurable and adaptable USB 2.0 OTG controller IP core, suitable for a wide range of applications.

Overview

Our company offers a highly configurable and adaptable USB 2.0 OTG controller IP core, suitable for a wide range of applications. This controller adheres to the latest industry standards (USB 2.0 and USB OTG) and works seamlessly with existing Windows, Linux, and Android drivers in host mode, minimizing software development effort and risks. It boasts multiple interface options for various systems and offers the flexibility to connect single devices directly or manage multiple devices via hubs. Additionally, optional features like a high-performance DMA engine and a dedicated processor block can be included to optimize performance and reduce development time in device mode. Overall, this versatile controller empowers developers with a wide range of functionalities and customization options, catering to both basic and advanced needs.

Key features

- Support SW controlled host/device role switching.

- Support Fullspeed and Lowspeed

- Support Control, Bulk, Interrupt and Isochronous Transfer Types

- Support L1/L2 power saving modes for USB 2.0 port

- Support Hardware LMP Capability and BESL LMP Capability for USB 2.0 ports in host mode

- Support MSI/MSI-X Interrupts and Legacy Interrupt

- Fully Support for Isochronous Transfer error handling, support error conditions like Isochronous Buffer Overrun, Bandwidth Overrun, Missed Service Error, Ring Overrun/Underrun, Parameter Error, etc. in host mode

- Fully Support for Event Data TRB, multiple Event TRBs can be used in one TD in host mode

- Fully Support for Hardware Bandwidth Management, support error conditions like Resource Error, Bandwidth Error and Secondary

- Bandwidth Error in host mode

- xHCI-like ring management, TRB definitions and doorbell mechanism in device mode

- Low-MIPS Operational Model.

- Pipelined transfer mechanism to achieve continuous data streaming

- Innovative Active TRB Prefetching technology to eliminate TRB access latency and improve system performance

- Dynamically reconfigurable Endpoint type, software can reconfigure the same Physical Endpoint to operate as Bulk, Interrupt or Isochronous EP

- Dynamic data buffer allocation for all endpoints,Tx/Rx Data Buffers can be shared by endpoints to optimize RAM usage

- Configurable number of supported device slots (up to 64) in host mode

- Configurable number of supported active Endpoints (up to 128) in host mode and Device mode

- Configurable numbers of USB 2.0 ports in host mode

- Configurable system bus type (AXI4/AXI3/AHB/APB) and width Configurable 2.0 PHY type (PIPE/UTMI+/ULPI) and width.

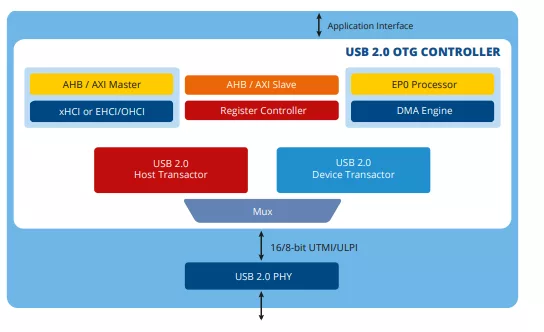

Block Diagram

USB 2.0 OTG Controller IP block diagram

What’s Included?

- The USB 2.0 OTG Controller interface is available in Source and netlist products.

- The Source product is delivered in plain text Verilog. If needed VHDL, SystemC code can also be provided.

- Firmware code and Linux driver package

- Documentation contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Part Number

USB 2.0 OTG Controller IP

Vendor

T2M GmbH

Provider

T2M GmbH

T2M GmbH is the leading Global Technology Company supplying state of the art complex semiconductor connectivity IPs and KGDs, enabling the creation of complex connected devices for Mobile, IoT and Wearable markets.

T2M's unique SoC White Box IPs are the design database of mass production RF connectivity chips supporting standards including Wifi, BT, BLE, Zigbee, NFC, LTE, GSM, GNS. They are available in source code as well as KGD for SIP / modules.

With offices in USA, Europe, China, Taiwan, South Korea, Japan, Singapore and India, T2M’s highly experienced team provides local support, accelerating product development and Time 2 Market.

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

In addition to performance and interoperability, achieving low power has been one of the requirements for industry standards specifications. Some of the key specifications like Universal Serial Bus (USB), PCI Express (PCIe), and MIPI have defined power saving features for burst traffic. This whitepaper explains how Synopsys USB IP offers low power using various low power states that go beyond the basic features.

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

Gervais Fong, Synopsys

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Sharmion Kerley, MIPI Alliance

Frequently asked questions about USB IP cores

What is USB 2.0 OTG High / Full / Low- Speed Dual Role IP Core?

USB 2.0 OTG High / Full / Low- Speed Dual Role IP Core is a USB IP core from T2M GmbH listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.