UniPro℠ Controller IP Core

To address the explosive growth in the mobile industry, the Mobile Industry Processor Interface (MIPI) Alliance was created to de…

Overview

To address the explosive growth in the mobile industry, the Mobile Industry Processor Interface (MIPI) Alliance was created to define and promote open standards for interfaces to mobile application processors. The Unified Protocol (UniPro) is one in a family of standards addressing the mobile market.

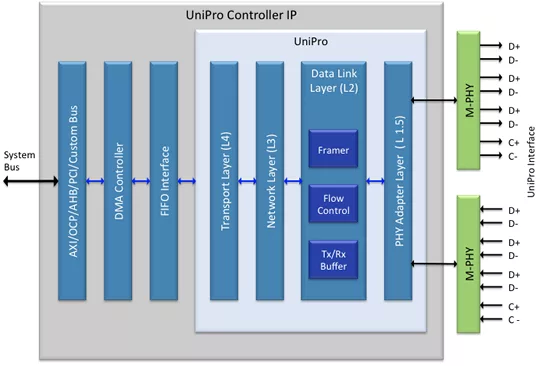

The UniPro Controller IP core is fully compliant with the UniPro specification version 1.6 and supports the physical adapter layer of the M-PHY® specification. MIPI UniPro is a high-performance, chip-to-chip, serial interconnect bus for mobile applications. Designed to support up to 5Gbps per data lane, it is scalable from one to four bidirectional lanes. To achieve optimal performance the Arasan UniPro Controller implements the following layers in hardware:

- Physical adapter layer

- Data link layer

- Network layer

- Transport layer

TC0 and TC1 traffic classes are handled on a priority-based transmission, and additional features include support of multiple power modes, error detection and handling, and data transmission preemption.

Unique to the Arasan controller is optional support that utilizes end-to-end flow control within UniPro to maximize transmission throughput and efficiency. Designed specifically for applications such as mobile phones, portable handheld media players, and mobile terminals, UniPro provides the high-speed connectivity needed between the applications processor and application devices such as wireless modules, graphics processors, multimedia accelerators, and storage subsystems. Targeted specifically for mobile phones, UniPro will be the high-speed chip connection of choice moving forward.

Key features

- MIPI UniPro Compliant

- MIPI M-PHY Version 3.0

- Multi-lane: one to four

- Up to 5Gbps per lane

- Package base protocol

- Device Independent

- Priority-based traffic classes (TC0 & TC1)

- Preemption support during data frame transmission

- Autonomous error detection and handling

- Multiple power modes

Layer Support

- PHY Adapter (L1.5)

- Data Link (L2)

- Network Layer (L3)

- Transport Layer (L4)

Interfaces

- AHB

- AXI

- OCP

- Custom

Block Diagram

Benefits

- Fully compliant core with proven silicon

- Premier direct support from Arasan IP core designers

- Easy-to-use industry standard test environment

- Unencrypted source code allows easy implementation

- Customer training available

- Reuse Methodology Manual guidelines (RMM) compliant verilog code ensured using Spyglas

What’s Included?

- RMM-compliant synthesizable RTL design in Verilog

- Easy-to-use test environment

- Synthesis scripts

- Technical documents

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UniPro IP core

Universal Flash Storage: Mobilize Your Data

Vertically Integrated MIPI Solutions

High Speed Memory in Smart Phones: MIPI UniPro v1.8 for JEDEC UFS v3.0

MIPI UniPro: Major Differentiating Features, Benefits and Verification Challenges

Specification Ambiguities of MIPI UniPro v1.41 clarified in MIPI UniPro v1.6

Frequently asked questions about UniPro IP cores

What is UniPro℠ Controller IP Core?

UniPro℠ Controller IP Core is a UniPro IP core from Arasan Chip Systems Inc. listed on Semi IP Hub.

How should engineers evaluate this UniPro?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UniPro IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.