MIPI Unipro Synthesizable Transactor

MIPI UniPro Synthesizable Transactor provides a smart way to verify the MIPI UniPro component of a SOC or a ASIC in Emulator or F…

Overview

MIPI UniPro Synthesizable Transactor provides a smart way to verify the MIPI UniPro component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's MIPI UniPro Synthesizable Transactor is fully compliant with standard MIPI UniPro Specification and provides the following features.

Key features

- Supports MIPI UniPro specification 1.41, 1.6 and 1.8

- Supports MIPI MPHY specification 3.0 and 4.1

- Supports data control at each layer of UniPro Specification for easy debug

- Supports multiple connections in L4 Layer and L4 segments

- Supports all valid segment sizes in L4 Layer

- Supports invalid field value insertion and detection in L4 Layer

- Supports end to end flow control at L4 layer

- Supports CPort arbitration at both segment level and packet level

- Supports Layer 3 error injection and detection

- Supports L2 data frames and control frames

- Supports injection of Errors and detection of errors in L2 data frames and control frame to test all cases as per specs

- Supports preemption and preemption error injection for L2 data frames

- Phy layer supports MPHY serial, MPHY RMMI (10, 20, 40 bit) Interface

- Phy layer supports multi lanes, Type-I and all power modes for Mphy

- Supports all types lane mapping (Lane 0 mapped to 1, 2, 3 etc)

- Supports error injection of all PACP frames

- Periodic deskew pattern injection, filler injections supported

- Supports link startup as per specs

- Supports Qos monitoring features

- Various types of error injection during LSS supported

- Various types of errors in PACP request and responses frames

- Supports CPort buffer based E2E checking

- Supports Scrambler, Skip pattern insertion as per specs

- Supports fine grain control and when flow control needs to be done and how to respond to flow control

- Supports M-PHY physical layer support with RMMI

- Supports up to four M-PHY lanes

- Supports Scrambler, SKIP insertion and Marker 2 extension

- Supports both data link layer frames:

- Data Frames

- Control Frames

- Supports PHY layer features:

- Transmission and reception of encoded PHY symbols

- Transmission of PHY IDLE symbols when no data is supplied

- Detection of PHY IDLE symbols

- Method to re-initialize the forward Link to overcome error situations

- Provision of different power modes and a method to signal them from transmitter to receiver

- Clock recovery

- Supports PHY adapter layer features:

- Transmission and reception of Data Link layer control symbols and data symbols via underlying PHY

- Lane distribution and merging in multi-lane ports

- Provision of MIPI UniPro power management operating modes

- (Re-)Initialization of the PHY TX path

- Transmit lane connect/disconnected features

- One lane mapping to different lanes

- Various kind of errors injects in LSS, PA Layer for various operation

- Supports Data Link layer features:

- Frame composition

- Frame decomposition

- Buffering Mechanism

- Frame preemption

- Triggering of PHY initialization

- Fine grain testing of flow control

- Two traffic classes by priority-based arbitration

- Various preemption error injections

- Creating all cases of error injection for L2 layer

- Error injection in PA_init process

- Detect various protocol errors

- Supports Network layer features:

- Packet composition and packet decomposition

- Packet format recognition

- Traffic Class

- Error handling

- Supports Transport layer features:

- Segmentation and Reassembly

- Segment Composition and Segment Decomposition

- Segment format recognition

- Connections management

- End-to-End flow-control

- Error handling

- Different CPort arbitration algorithms supported

- Various kinds of error injection:

- Various kinds of error detection

- CPort Buffer management to mimic real life cases

- Supports complete DME functionality

- Supports all layer error injection and detection

- Supports various kind of TX and RX errors generation and detection on M-PHY:

- Disparity errors

- Invalid control chars

- Invalid sync sequencer errors

- Timeout conditions injections

- CRC errors

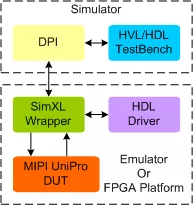

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the MIPI UniPro testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UniPro IP core

MIPI UniPro: Major Differentiating Features, Benefits and Verification Challenges

Specification Ambiguities of MIPI UniPro v1.41 clarified in MIPI UniPro v1.6

Technical Comparison: MIPI UniPro 1.6 vs MIPI UniPro 1.41

MIPI Unipro Transport Layer (L4) - An Introduction

MIPI UniPro: Comprehensive Verification Checklist

Frequently asked questions about UniPro IP cores

What is MIPI Unipro Synthesizable Transactor?

MIPI Unipro Synthesizable Transactor is a UniPro IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this UniPro?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UniPro IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.