SPI (Serial Peripheral Interface) Synthesizable Transactor

SPI (Serial Peripheral Interface) Synthesizable Transactor provides a smart way to verify the SPI component of a SOC or a ASIC in…

Overview

SPI (Serial Peripheral Interface) Synthesizable Transactor provides a smart way to verify the SPI component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's SPI Synthesizable Transactor is fully compliant with standard SPI Specification and provides the following features.

Key features

- Follows SPI basic specification as defined in SPI Block Guide V04.01

- Supports Master and Slave Mode

- Supports 3-wire,4-wire interface

- Supports SQI interface specification and common flash device models

- Supports data width from 4 bits to 64 bits

- Supports bus width 1 bit and 4 bit

- Slave device supported for SPI 3 wire are

- BOSCH SMB380

- RICOH R2033K

- Supports baud rate selection

- Supports internal clock division check

- Supports clock polarity selections

- Supports CPHA selection

- Supports single and burst transfer mode

- Supports on the fly generation of data

- Detects and reports the following errors

- Mode Fault error

- Supports constraints Randomization

- Supports glitch insertion and detection

- Status counters for various events on bus

- Supports single,dual and quad mode bus width operation

- Supports spansion DDR model

- SPI Slave can be configured as standard device or can use FIFO for data passing

- In standard model mode, Mater/Slave support different types of devices. Like FLASH, EEPROM, FRAM,RTC,SQI,MOTOROLA Mode,NS mode and TI mode(Precede and Coincide)

- Master contains rich set of commands for both standard device and FIFO model mode

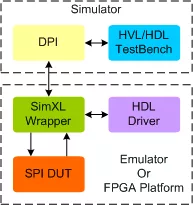

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the SPI testcases

- Examples showing how to connect and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation also contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SPI / QSPI XSPI IP core

Unleashing the Power of Communication: Exploring the XSPI Protocol and Arasan Chip Systems' XSPI IP Portfolio

Frequently asked questions about SPI / QSPI / xSPI IP cores

What is SPI (Serial Peripheral Interface) Synthesizable Transactor?

SPI (Serial Peripheral Interface) Synthesizable Transactor is a SPI / QSPI XSPI IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this SPI / QSPI XSPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPI / QSPI XSPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.