SPI/xSPI/QSPI/OSPI Verification IP

The SPI/xSPI/QSPI/OSPI Verification IP provides an effective & efficient way to verify the components interfacing with SPI/QSPI/O…

Overview

The SPI/xSPI/QSPI/OSPI Verification IP provides an effective & efficient way to verify the components interfacing with SPI/QSPI/OSPI interface of an ASIC/FPGA or SoC.

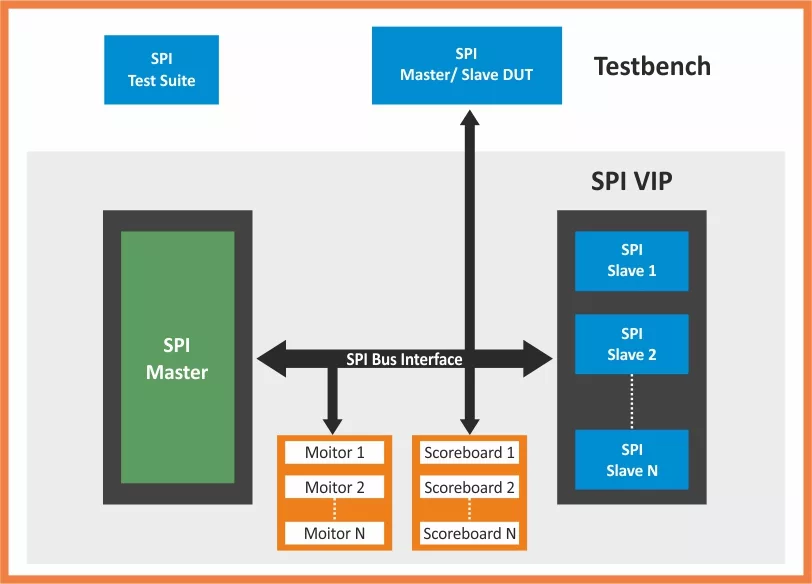

VIP environment encapsulates the SPI/xSPI/QSPI/OSPI compatible UVM based Master, compatible Slave, BUS monitor & Scoreboard. BUS monitor monitors all the transfers that are going on the SPI/xSPI/QSPI/OSPI bus. It verifies all the transfers for any protocol violation and displays an error message with the cause of the error, if an error occurs in the transfer. Protocol checks based on assertion checking are also done to enhance the capability of the bus monitor.

The VIP fully supports the out of box testing. User can plug in their DUT slave or DUT Master in this environment. Various test suites are provided for regressive testing. The user can also write his own test case according to his intention. This VIP is a lightweight with an easy plug-and-play interface so that there is no hit on the design time and the simulation time.

Key features

- SPI Available in UVM, System UVM, UVM.

- Error response types supported.

- Multi-Slave and Single-Master support.

- Rich set of configuration parameters for each individual Slave Agent

- Configurable wait states.

- Supports different memory update Mode Configurations.

- Rich set of configuration parameters for Master Agent

- Supports continuous or non-continuous read/write transmission.

- Rich set of configuration parameters to control SPI functionality.

- UVM status counters for various transfers on the bus

- SPI/QSPI/OSPI Verification IP comes with a complete test suite to test every feature of Motorola, Macronix, Windbond, Micron, and Samsung specifications.

- Simultaneous transfer from master and slave.

- Supports 8-bit/16-bit/32-bit shift registers for Tx/Rx.

- Supports an 8-bit/16-bit/32-bit bus interface.

- Supports two independent 32-bit wide transmit and receive FIFOs.

- Supports serial clock with programmable polarity and phase.

- Supports control of SPI operation during wait mode.

- Supports Single I/O, Dual I/O and Quad I/O, Extended I/O protocol.

- Supports DTR(Double Transfer Rate) mode.

- Supports Quad Input/output page program (4PP).

- Supports error logs with the descriptive cause of error or protocol violations.

- User Test Suite

Block Diagram

Benefits

- Available in native System Verilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity example for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment

What’s Included?

- SPI/QSPI/OSPI Master

- SPI/QSPI/OSPI Slave

- SPI/QSPI/OSPI Monitor

- SPI/QSPI/OSPI Scoreboard

- Test Suites (in Source Codes)

- Basic Test Suite

- Random Test Suite

- Error Test Suite

- User Test Suite

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about SPI / QSPI XSPI IP core

Unleashing the Power of Communication: Exploring the XSPI Protocol and Arasan Chip Systems' XSPI IP Portfolio

Frequently asked questions about SPI / QSPI / xSPI IP cores

What is SPI/xSPI/QSPI/OSPI Verification IP?

SPI/xSPI/QSPI/OSPI Verification IP is a SPI / QSPI XSPI IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this SPI / QSPI XSPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPI / QSPI XSPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.