Simulation VIP for Q-SPI

In production since 2018 for many production designs.The Cadence® Verification IP (VIP) for Quad SPI provides verification of Q-S…

Overview

In production since 2018 for many production designs.

The Cadence® Verification IP (VIP) for Quad SPI provides verification of Q-SPI NOR devices using the SPI protocol. The VIP for Q-SPI is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model.

Supported Specification: Features of all major vendors such as Micron, Macronix, Winbond, Cypress, GigaDevices, and ISSI.

Key features

- Device Density

- From 256Mb to 2Gb with frequency up to 166MHz

- Operation Mode

- Single I/O, Dual I/O, and Quad I/O (Q-SPI and QSPI) with single and double transfer rate (STR and DTR)

- RESET

- Supports Soft reset using the Reset command and Hard reset using the Reset Pin are available

- Device Identification

- Supports Read Q-SPI Serial Flash Discoverable parameter (Read SFDP command) and Device Identification and factory features using JEDEC-standard 3-byte signature, Extended device ID

- Configuration Capability

- Volatile and non-volatile configuration register settings to change the mode of the model, dummy cycle number for FAST read operation, and 3-byte or 4-byte addressing

- Fast Boot Feature

- Fast Boot feature support to provide the ability to automatically execute Read operation after Power on cycle or Reset without any Read command based on the configuration of Fast Boot register values

- Commands

- Supports READ, FAST READ, 2READ, DREAD, 4READ, QREAD and Burst Read for 16-byte, 32-byte, and 64-byte Wrap Bursts for Read commands

- Supports Quad Output, Quad I/O, DTR Quad Output, DTR Quad I/O, including all 4-Bytre Fast Read commands

- Supports PAGE Program, Dual Page Program, and Quad Page Program instructions

- Supports Quad Input, Extended Quad Input, 4-Bytes Quad Input, 4-Byte Extended Quad Input and DTR 4-Bytes Quad Input Fast Program

- Supports Bulk erase (Chip Erase), Sector erase uniform granularity and Sub-sector erase 4KB, 32KB, 64KB granularity

- Supports PROGRAM and ERASE SUSPEND operations

- Supports Device Input and Output timing and Variants memory operations timing

- Supports Configuration Registers: Volatile Configuration Register 1 and 2, Non-Volatile Configuration Register 1 and 2

- Deep Power Down Mode

- Does not accept commands except Release and Exit from the Deep Power Down Command

- Preamble Data Pattern

- Based on the PBE bit value, Selected Preamble Pattern will be inputted to the Dummy Cycles

- Security and Write Protection

- One-time program (OTP) array of 1024 bytes

- Status Register bits to control protection against program or erase of a contiguous range of sectors: Hardware and software control options, Advanced Sector Protection (ASP), Individual sector protection controlled by boot code or password, Block Protection define protected area size

- Additional Functionalities

- Execute-in-place (XIP), Data Learning Registers, High-performance Read mode

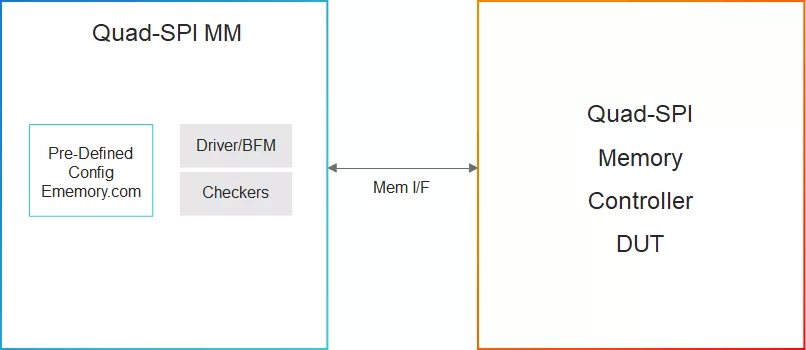

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SPI / QSPI XSPI IP core

Unleashing the Power of Communication: Exploring the XSPI Protocol and Arasan Chip Systems' XSPI IP Portfolio

Frequently asked questions about SPI / QSPI / xSPI IP cores

What is Simulation VIP for Q-SPI?

Simulation VIP for Q-SPI is a SPI / QSPI XSPI IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this SPI / QSPI XSPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPI / QSPI XSPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.