Simulation VIP for xSPI

xSPI in production since 2019 for many production designs.The Cadence® Memory Model Verification IP (VIP) for xSPI provides verif…

Overview

xSPI in production since 2019 for many production designs.

The Cadence® Memory Model Verification IP (VIP) for xSPI provides verification of xSPI (Expanded SPI) NOR flash devices using the SPI protocol. The VIP for xSPI is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model. The VIP for xSPI includes both support for xSPI and VIP for OSPI NOR.

Supported specification: JEDEC specifications: JESD251 Profile 1 v1.0, JESD251-A1, JESD252, and JESD216D and Memory Vendors specifications of ADESTO (DS_XP032_114G_122018), MICRON (tn1235_sfdp_mt35x Rev. B 10/18 EN - compliant to JESD216B ONLY), MACRONIX, (AN0726 Rev1 for MX66UM2G45G) and CYPRESS (002-18216, Rev:*M).

Key features

- xSPI Profile 1

- SPI (Read Zero Latency), DUAL (1-1-2, 1-2-2), Quad (As per JESD251-A1), and Octal modes Data Rate: STR and DTR

- Modes

- SPI-STR (1S-1S-1S), QUAD-STR (4S-4S-4S), OCTAL-STR(8S-8S-8S), and OCTAL-DTR (8D-8D-8D) modes

- Reset

- Software Reset Feature: Soft reset with reset enable (0x66) and reset command (0x99) with return to default protocol mode

- Modes Switching Commands

- Supports Command to enter OCTAL(E8h), QPI(38h), and SPI(FFh) modes

- Read modes

- Supports Read for SFDP Headers, Parameter Headers, and Parameter DWORDS, Page Read, Read Fast Wrapped, and Set up Read Wrapped

- Octal DTR mode

- Command Extension Feature for Octal DTR mode (8D-8D-8D)

- Program Operation

- Byte and Page Program, Program Suspend and Resume command

- Erase Operation

- Chip Erase and Block Erase (4, 32, 64, and 256 KB), Erase Suspend and Resume command

- Deep Power Down

- Supports Deep Power Down feature

- SCCR

- Write status control register command to all register fields, volatile and nonvolatile offset address, register bits and Read status register

- Addressing Capability

- 3-byte and 4-byte address modes. Enter and Exit 4-byte mode

- Shared Pin Feature

- Shared IO3 Pin with Hold Pin and Shared IO3 Pin with Reset Pin

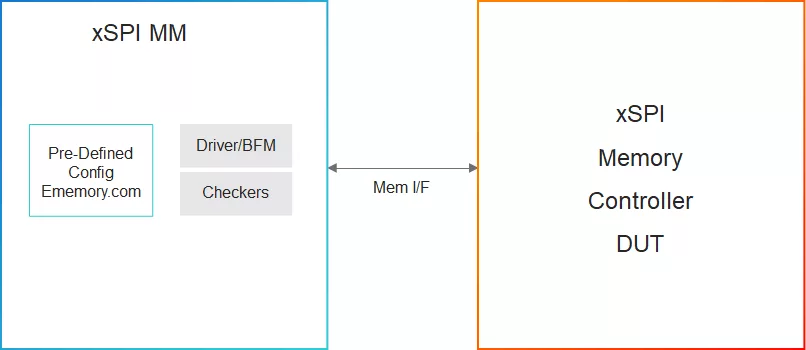

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SPI / QSPI XSPI IP core

Unleashing the Power of Communication: Exploring the XSPI Protocol and Arasan Chip Systems' XSPI IP Portfolio

Frequently asked questions about SPI / QSPI / xSPI IP cores

What is Simulation VIP for xSPI?

Simulation VIP for xSPI is a SPI / QSPI XSPI IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this SPI / QSPI XSPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPI / QSPI XSPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.