Simulation VIP for SPI NAND

In production since 2016 for many production designs.

Overview

In production since 2016 for many production designs.

The Cadence® Memory Model Verification IP (VIP) for Flash SPI NAND provides verification of Flash NAND devices using the SPI protocol. It provides a mature, highly capable compliance verification solution applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification. The VIP for SPI NAND is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model.

Supported specification: SPI Nand features of the following vendors specifications: GigaDevices, Macronix, Micron, Winbond, ESMT, XTX, ATO and ZENTEL.

Key features

- Operation Modes

- Single I/O, Dual I/O, and Quad I/O (Q-SPI and QSPI) and serial mode 0 and mode 3

- Pins

- HOLD# and WP# Pins functionalities

- Reset

- Support of reset commands: 0xFF, 0xFE which put the memory device into a known condition and to abort the command sequence in progress

- Read ID

- Support of Read ID command: 0x9F which read the identifier code (Manufacturer ID and device ID) of the memory device

- Commands

- Support of Set (0x1F) and Get (0x0F) feature: Alter device behavior for Block Protection, Lock, OTP and Configuration, and Die select register

- Various Read commands: Page Read to Cache (0x13), Read from Cache(0x03, 0x0B Single I/O and SPI)

- Various Program commands: Program Load (0x02), Program Execute (0x10), Program Load Random Data (0x84, 0x34, 0xC4)

- Block Erase 0xD8 command

- Page Cache Random

- Supports of 0x30, 0xBB (Dual IO), 0xEB (Quad I/O), read page(s) in sequential/random order (Micron only)

- Quad SPI

- Quad Input and Output commands quadruple the transfer for Read and Program command, Quad SPI Mode uses DQ [3:0].

- Read commands: Read from Cache Quad IO, Read from Cache x4

- Program commands: Program Load x4, Program Load Random Data x4

- Permanent Block Lock Protection

- 0x2C, can lock 48 blocks per die permanently (Micron)

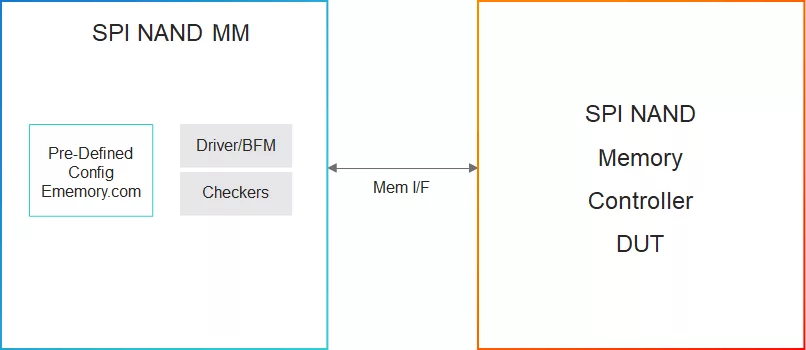

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SPI / QSPI XSPI IP core

Unleashing the Power of Communication: Exploring the XSPI Protocol and Arasan Chip Systems' XSPI IP Portfolio

Frequently asked questions about SPI / QSPI / xSPI IP cores

What is Simulation VIP for SPI NAND?

Simulation VIP for SPI NAND is a SPI / QSPI XSPI IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this SPI / QSPI XSPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPI / QSPI XSPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.