SPI/EEPROM Verification IP

SPI/EEPROM Verification IP provides an smart way to verify the serial synchronous communication protocol.The SmartDV's SPI/EEPROM…

Overview

SPI/EEPROM Verification IP provides an smart way to verify the serial synchronous communication protocol.The SmartDV's SPI/EEPROM Verification IP is fully compliant with SPI Block Guide V04.01 of the EEPROM's Atmel AT25128A,AT25256A eeprom and Saifun SA25C020 eeprom Specification and provides the following features. It can work with Verilog HDL environment and works with all Verilog simulators that are support SystemVerilog.

SPI/EEPROM Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

SPI/EEPROM Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Follows EEPROM basic specification as defined in Atmel AT25128A,AT25256A

- EEPROM and Saifun SA25C020 EEPROM

- Supports SPI Modes 0 (0,0) and 3 (1,1)

- Supports 64-byte Page Mode and Byte Write Operation

- Supports Block Write Protection for Protect Quarter, Half or Entire Array

- Supports Write Protect (WP) Pin and Write Disable Instructions

- Supports for Data Protection

- Supports Byte and Page Write Operation:

- Supports customized single/dual/quad modes for Command, Address and Data phase

- Supports configurable dummy cycles

- Supports configurable memory density

- Supports backdoor access for memory and registers

- Built in functional coverage analysis.

- Supports Callbacks in master, slave and monitor for modifying, and sampling data/cmd on SPI/EEPROM bus.

- SPI/EEPROM Slave can be configured as standard device or can use FIFO for data passing.

- Master contains rich set of commands for both standard device and FIFO model mode.

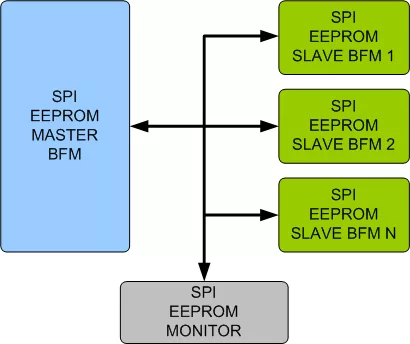

Block Diagram

Benefits

- Faster testbench development and more complete verification of SPI/EEPROM designs.

- Easy to use command interface simplifies testbench control and configuration of slave and master.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the SPI/EEPROM testcases.

- Examples showing how to connect various components, and usage of Master, Slave and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SPI / QSPI XSPI IP core

Unleashing the Power of Communication: Exploring the XSPI Protocol and Arasan Chip Systems' XSPI IP Portfolio

Frequently asked questions about SPI / QSPI / xSPI IP cores

What is SPI/EEPROM Verification IP?

SPI/EEPROM Verification IP is a SPI / QSPI XSPI IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this SPI / QSPI XSPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPI / QSPI XSPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.