Simulation VIP for HDMI

In production since 2011 on many production designs.The Cadence® Verification IP (VIP) for HDMI provides a mature, capable compli…

Overview

In production since 2011 on many production designs.

The Cadence® Verification IP (VIP) for HDMI provides a mature, highly capable compliance verification solution for the HDMI Protocol. The VIP for HDMI supports simulation and hardware acceleration platforms making it applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification. The VIP is compatible with the industry-standard Universal Verification Methodology (UVM) and runs on all leading simulators.

The High-Definition Multimedia Interface (HDMI) is an audio/video (A/V) transmission protocol, which is omnipresent in consumer electronics, PC, and mobile products. HDMI supports two kinds of devices: SOURCE, which transmits A/V on HDMI cable, and SINK, which receives and decodes A/V.

Supported specifications: HDMI VIP supports HDMI Protocol versions 1.4b, 2.0a, and 2.1.

Key features

- 3D – Capability

- Supports various 3D video frame formats

- 4K x 2K Resolution

- Supports 4Kx2K video frame formats

- 3D - Guarantee Interoperability for 25Hz Formats

- Supports 3D video formats for 25Hz frames

- 3D - Indication of Independent View

- Supports configuration of 3D Video extension registers in HDMI LLC Vendor-Specific InfoFrame Packet

- 3D - Support Dual-View

- Supports configuration of 3D Video extension registers in HDMI LLC Vendor-Specific InfoFrame Packet

- 3D - Support OSD Disparity Indication

- Supports configuration of 3D Video extension registers in HDMI LLC Vendor-Specific InfoFrame Packet

- 21x9

- Supports all 21:9 video formats defined by CEA-861-F specifications

- Audio Extensions

- Supports 3D Audio and Multi-stream Audio

- Custom Frame Formats

- Supports Custom Frame formats that allow the user to configure frame formats that are DUT specific and not defined in the specification

- Character Error Detection (CED)

- Supports the mechanism for detecting and reporting character errors

- Deep Color Modes

- Supports B24, B30, B36, B48 deep color modes

- Direct Data Channel (DDC)

- Supports the DDC channel, which is used by an HDMI source to determine the capabilities and characteristics of the sink by reading the E-EDID data structure

- Expanded Color Spaces

- Supports different types of extended color space exclusively defined within the HDMI specification

- HDMI CTS 2.0 Compliance

- Supports HDMI CTS 2.0 compliance checks

- HDMI Packets

- Supports all packet types defined in the HDMI Specification 2.0

- HDMI/DVI Mode

- Supports both HDMI and DVI mode of operation

- In the HDMI mode of operation, the HDMI frame consists of video data, control data, and packets, while in DVI mode, the HDMI frame consists of video data and control period only

- HDR

- Supports HDR dynamic range and mastering infoframe defined in CEA 861.3

- Supports HDR Static Metadata Block defined in CEA 861.3

- HDCP 1.4

- Supports different types of HDCP encryption mode, supports Key Selection Vectors for transmitter and receiver

- Supports transmission and reception of HDCP private keys

- Supports Authentication bypass

- Supports both EESS and OESS modes

- HDCP 2.2

- Supports Authentication and Key Exchange (with and without pairing)

- Supports locality check

- Supports Session Key Exchange

- Supports Transmitter/Receiver State Machines

- Supports Link Integrity Check

- Supports Encryption (Cipher and Enhanced Encryption Status Signaling)

- Pixel Encoding

- Supports RGB, YCbCr 4:4:4, and YCbCr 4:2:2 pixel encodings

- Error Injection

- Support for dynamic/random error injection at multiple levels of hierarchy, i.e., Data Island, Video Pixel, Control, etc. for SOURCE VIP. Additional Error Injection scenarios can be generated through VIP callbacks

- Scrambling for EMI/RFI Reduction

- Supports 340Mcsc to 600Mcsc TMDS Character Rate

- SCDC

- Supports SCDC registers

- Supports Read Request by slave

- Source and Sink

- Supports verification of both Source (TX) and Sink (RX) device types

- Serial and Symbol Interfaces

- Supports Serial and Symbol interface types

- TMDS

- Supports TMDS bit period/TMDS clock-period ration of 1/40

- YCbCr

- Supports 4:2:0 based pixel encoding and frame packing/unpacking

- CEC

- Support for CEC 2.0

- Reset

- Dynamic software reset capability

- Fixed Rate Link (FRL)

- Operation at 3, 6, 8, 10, and 12Gbps

- 3/4 Lane Operation

- FRL Packetization

- Link Training

- LTP 1, 2, 4 – 8

- RS-FEC

- FRL Character and Super Blocks

- Data Flow Metering (DFM) – Capacity computation for uncompressed video and variations check for excess FRL bandwidth.

- Scrambling LFSR

- 16b/18b coding

- FRL Video Transmission

- Supports uncompressed FRL video transmission 1K, 4K, 5K, 8K and 10K

- Supports non-standard video frames

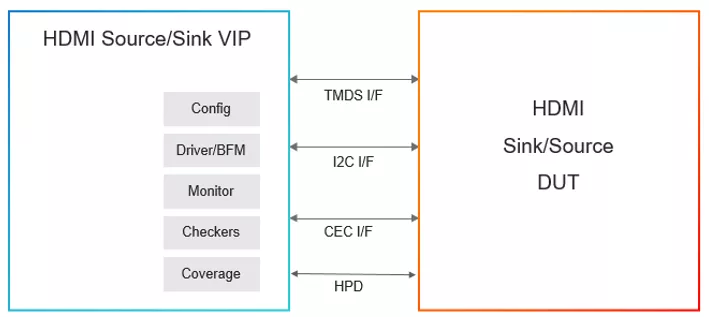

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about HDMI IP core

The Power Of HDMI ARC

Dynamic HDR in HDMI 2.1: The Ideal Display for TV and Mobiles

HDMI: How Scrambling Enables Higher Data Rates

High Resolution Displays for Mobile, TV, PC and Automotive Enabled by DSC 1.2 in HDMI 2.1

HDMI 2.1: How it Became the Most Popular Display Interface

Frequently asked questions about HDMI IP cores

What is Simulation VIP for HDMI?

Simulation VIP for HDMI is a HDMI IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this HDMI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this HDMI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.