Simulation VIP for Ethernet TSN

Mature and capable compliance verification solution.The Cadence® Verification IP (VIP) for Ethernet Time-Sensitive Networks (TSN)…

Overview

Mature and highly capable compliance verification solution.

The Cadence<sub>®</sub> Verification IP (VIP) for Ethernet Time-Sensitive Networks (TSN) provides a mature, highly capable compliance verification solution for the TSN protocol stack incorporating bus functional model (BFM) and integrated protocol checkers and coverage. The VIP for Ethernet TSN is designed for easy integration in test benches at IP, system-on-chip (SoC), and system levels, helping to reduce time to test, accelerate verification closure, and ensure end-product quality. The VIP for Ethernet TSN is compatible with the industry-standard Universal Verification Methodology (UVM) and runs on all leading simulators.

TSN is a family of protocols primarily of the data link layer and a couple of layers above it in the OSI Communication model, which defines the behavior of communication in low-latency systems like automotive, industrial automation, and professional audio/video devices. These networks are usually designed to work over a framework of Ethernet MAC and PHY layers.

Supported specifications: IEEE 802.1 AS-2011, Qbu, Qav, Qbv, Qat, AE, CB, IEEE 802.3br, IEEE 1722, ISO 61883, TCP, UDP, IPv4, and IPv6 protocols.

Key features

- IEEE P802.1AS-2011

- Transmissions: PTP over Ethernet, PTP over IPoE

- Clock synchronization between different time-aware systems

- Best Master Clock Algorithm

- Time-stamping unit

- Receipt timeout mechanism

- Peer Delay mechanism for link propagation delay measurement

- Message types supported: Sync and Follow_Up, Pdelay_Req, Pdelay_Resp and Pdelay_Resp_Follow_Up, Announce message and Signaling message

- Protocol checkers for the frame fields at the transmitter and receiver side

- IEEE 1588-2002 v1

- Transmission and reception for the frames: Sync, Follow_Up, Delay_Req, Delay_Resp

- Transmission of PTP over Ethernet, PTP over IPoE

- Protocol checkers for the frame fields at the receiver side

- IEEE 1588-2008 v2

- Transmission and reception for the frames: Announce, Sync, Delay_Req, Pdelay_Req, Follow_Up, Delay_Resp, Pdelay_Resp, Pdelay_Resp_Follow_Up, Signaling

- Transmission of PTP over Ethernet, PTP over IPoE

- Protocol checkers for the frame fields at the receiver side

- Credit-Based Shaping

- Credit-based scheduling algorithm

- Scheduled, best effort, and reserved queues

- Bandwidth allocation through credit-shaping mechanism

- Up to 10G speed

- Time-Aware Shaper

- Enhancements for scheduled traffic that allow transmission from each queue to be scheduled relative to a known timescale

- Timing-based schedule algorithm

- Transmission selection using transmission gates associated with a priority queue

- IEEE 1722 AVTP

- Audio/video packet sub-types which are encapsulated in the form of AVTPDUs to be carried over AVTP networks

- Protocol sub-types supported by the VIP for transport of AVTPDUs are 61883_IIDC, MMA, MAAP

- Preemption

- Hold mechanism

- Priority table configuration

- Express and preemptive frame scheduling

- Interspersing

- IET Verification

- Frames, transmission, and reception

- Fragmentation of Ethernet frame when preempted

- MACSec

- MacSec IEEE 802.1AE-2018 specification

- Cipher suites : AES-GCM-128, AES-GCM-256, AES-GCM-XPN-128, AES-GCM-XPN-256

- Pre-shared key

- Authentication and integrity modes

- Replay Protection

- Up to 800G

- MSRP

- Multiple Reservation Protocol (MRP)

- Multiple Stream Reservation Protocol using MRP except for domain discovery

- Up to 1G speed

- Transport Layer

- Encapsulation/extraction of TCP and UDP segments

- Network Layer

- Encapsulation/extraction of Internet Protocol Version 4/6 (IPv4/IPv6) packet

- Layer 2 Packet

- Encapsulation and extraction of MPLS (Unicast and Multicast) label, FC and FIP packets and SNAP header

- FRER

- Transmission of replicated packets in multiple streams.

- Vector and Match Recovery Algorithms for frame elimination.

- Appropriate Checkers and Coverage are available.

- PSFP

- Stream Filters, Stream Gates, Flow Meters

- Bandwidth profile Algorithm (Metering Algorithm)

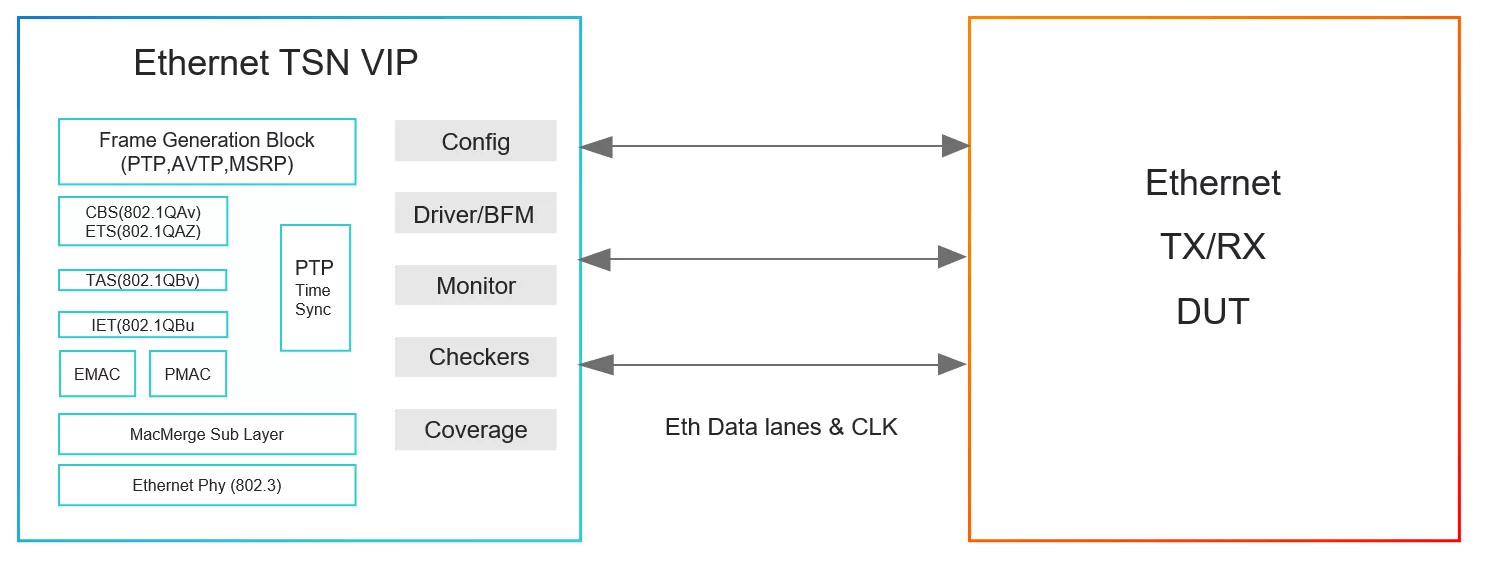

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is Simulation VIP for Ethernet TSN?

Simulation VIP for Ethernet TSN is a Ethernet IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.