Ethernet Synthesizable Transactor

The Ethernet Synthesizable Transactor verifies Ethernet interfaces.

Overview

The Ethernet Synthesizable Transactor verifies Ethernet interfaces. Ethernet is build on top of it to make it robust. Ethernet Synthesizable Transactor provides a smart way to verify the Ethernet component of a SOC or a ASIC in Emulator or FPGA platform. Ethernet Synthesizable Transactor is developed by experts in networking, who have developed networking products in companies like Intel, Cortina-Systems, Emulex, Cisco. We know what it takes to verify a networking product.

Key features

- Supports Full MII/RMII/SMII TX/RX functionality

- Supports Mac control and data frames support

- Ability to generate VLAN tagged and Priority tagged frames

- Supports Pause frame detection and generation

- Supports Jumbo frames

- Supports Under and oversize frame

- Supports 1G:

- Supports GMII

- Supports TBI (i.e Output of 8b/10b PCS)

- Supports SGMII/SGMII_TBI as per specification 1.8

- Supports QSGMII as per specification 1.2

- Supports USGMII as per specification 3.0 and 3.1(5G and 10G)

- Supports RGMII/RTBI as per specification 2.0

- Supports 1000Base-KX

- Supports clause 73 backplane auto-negotiation for 1000Base-KX

- Supports clause 37 auto-negotiation

- Supports SGMII auto-negotiation

- Supports QSGMII auto-negotiation

- Supports USGMII auto-negotiation and packets

- Supports full duplex and half duplex of operation

- Supports 10G as per 802.3:

- Supports XGMII

- Supports XTBI (i.e Output of 8b/10b PCS)

- Supports XAUI, RXAUI,DXAUI and 10GBASE-KX4

- Supports 10GBASE-KR with scrambler

- Supports FEC for 10GBase-KR

- Supports single port USXGMII as per specification 2.5

- Supports multi-port USXGMII as per specification 2.2

- Supports scrambler

- Supports backplane auto-negotiation for 10GBase-KX4 and 10GBase-KR

- Supports 25G and 50G Speeds:

- Supports 25GBase_R

- Supports 25GBase_KR

- Supports 50GBase_KR

- Supports 50GBase_KR2

- Supports FEC

- Supports scrambler

- Supports backplane auto-negotiation

- Supports 40G as per 802.3ba:

- Supports XLGMII

- Supports 40GBase-KR4/40GBase-CR4/40GBase-SR4/40GBase-LR4

- Supports 40GBase-R

- Supports 40GBase-KR2

- Supports FEC

- Supports scrambler

- Supports backplane auto-negotiation

- Supports 100G as per 802.3ba and 802.3bj:

- Supports CGMII

- Supports CAUI4

- Supports 100GBase-KR10/100GBase-CR10/100GBase-SR10

- Supports 100GBase-ER4/100GBase-LR4

- Supports 100GBase-KR4

- Supports 100GBase-KR2

- Supports 100GBase-KR

- Supports 100GBase-R

- Supports FEC for clause 91(RS-FEC)

- Supports scrambler

- Supports backplane auto-negotiation

- Supports 200G and 400G as per 802.3bs:

- Supports 200GBase_KR8

- Supports 200GBase_KR4

- Supports 200GBase_KR2

- Supports 400GBase_KR4

- Supports 400GBase_KR8

- Supports 400GBase_KR16

- Supports FEC

- Supports scrambler

- Supports backplane auto-negotiation

- PCS to serdes interface supports all widths

- Supports MDIO slave and master model as per Clause 22 and Clause 45

- Full support for IEEE 1588-2002 and IEEE 1588-2008

- Supports all types of TX and RX errors insertion/detection at each layer

- Supports Under and oversize frame

- CRC errors

- Framing errors

- Pause frame errors

- Disparity and Auto-negotiation errors

- Invalid code group insertion

- Invalid /K/ characters insertion

- Lane Skew insertion

- Invalid AN sequence error insertion

- Missing /K/ characters for packet boundaries

- Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations

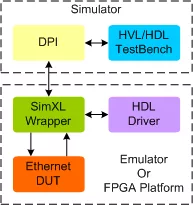

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the Ethernet testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is Ethernet Synthesizable Transactor?

Ethernet Synthesizable Transactor is a Ethernet IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.