Simulation VIP for AMBA APB

Cadence provides a mature and comprehensive Verification IP (VIP) for the Peripheral Bus (APB) specification, which is part of th…

Overview

Cadence provides a mature and comprehensive Verification IP (VIP) for the Advanced Peripheral Bus (APB) specification, which is part of the Arm® AMBA® family of protocols. Incorporating the latest protocol updates, the Cadence® Verification IP for APB provides a complete bus functional model (BFM), integrated automatic protocol checks, and coverage model. Designed for easy integration in testbenches at IP, system-on-chip (SoC), and system levels, the VIP for APB helps you reduce time to test, accelerate verification closure, and ensure end-product quality. Cadence provides a solution for interconnect verification that verifies the correctness and completeness of data. The VIP is compatible with the industry-standard Universal Verification Methodology (UVM) and runs on all leading simulators.

Supported specifications: AMBA 2 APB, AMBA 3 APB, AMBA 4 APB, AMBA 5 APB issue D and E.

Key features

- Data and Address Widths

- All legal data and address widths

- Automatic Completer Responses

- Support to use automatic Completer responses

- Delay Control

- Control the delay between the items on the channels

- Multiple Agents

- Supports any number of agents

- Requester Transfer Signal Control

- Control the values of the signals in the write data channel

- Completer Response Control

- Control over the values of the signals in the read data channel

- Completer Memory Emulation

- Data consistency check for Completers using memories

- Transaction Types

- Monitoring and driving of all read and write transactions

- Pprot and Pstrb

- Strobe and Protection Type signals as defined in APB4 spec v2.0

- Completer Responses

- PLSVERR signal as defined in APB4 spec v2.0 and in APB3

- Completer Response Wait State

- Completer Response Wait State as defined in APB4 spec v2.0 and in APB3

- Support for Parity

- Parity support for each signal

- APB5 Issue D

- User Signaling, Wakeup Support

- APB5 Issue E

- Root Realm Management, SubSysId support

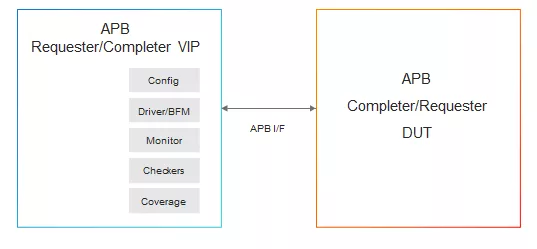

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Protocol Bridge IP core

Script/simulation approach speeds SoC verification

A comparison of Network-on-Chip and Busses

Synthesizable verification IP speeds design cycle

Synthesizable Verification IP

IP Core for an H.264 Decoder SoC

Frequently asked questions about Protocol Bridge IP cores

What is Simulation VIP for AMBA APB?

Simulation VIP for AMBA APB is a Protocol Bridge IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Protocol Bridge?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Protocol Bridge IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.