Power Management Unit

PMU IP includes following components: Bandgap reference voltage source, reference current sources and reference frequency generat…

Overview

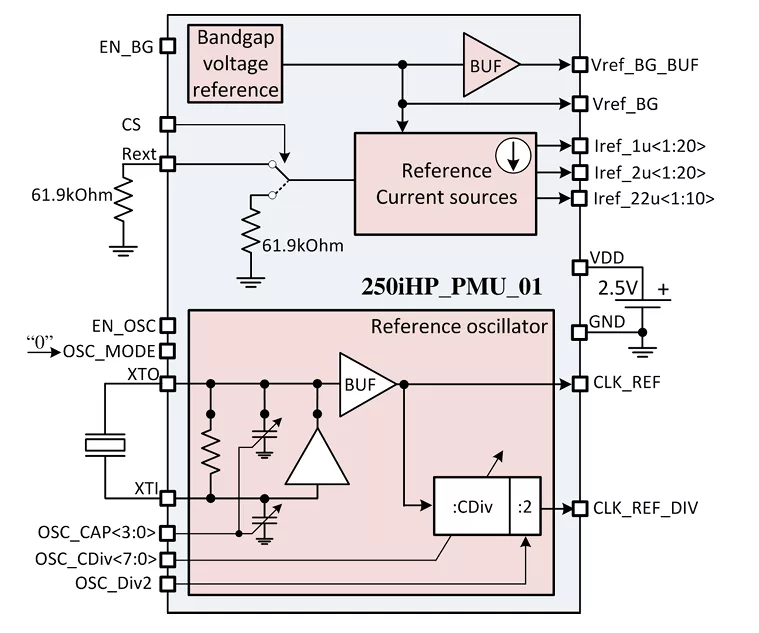

PMU IP includes following components: Bandgap reference voltage source, reference current sources and reference frequency generator. Bandgap source forms temperature, power supply and process variations independent voltage.

Reference current sources provide stable output currents which are independent of process/voltage/temperature variations if external resistor is used (CS = “0”) or dependent of process corner and temperature of internal resistor rppd (CS = “1”).

Reference frequency generator could operate in two modes: XTALL mode (OSC_MODE = “0”) and TCXO mode (OSC_MODE = “1”). In XTALL mode external resonator is used, while in TCXO mode external TCXO provides input frequency signal, which is buffered and additionally divided. There are two output frequencies: undivided reference frequency (CLK_REF output) and programmable (OSC_CDiv<7:0>) divided frequency (CLK_REF_DIV). To achieve 50% duty cycle at CLK_REF_DIV output there is additional division-by-two stage embedded in frequency divider, which is turned on by OSC_Div2 = “1”.

Key features

- iHP SG25H4 SiGe BiCMOS 0.25 um

- Bandgap voltage source 1.12 V

- Constant current source

- 500 Hz to 140 kHz frequency generator

- Standby mode

- Portable to other technologies (upon request)

Block Diagram

Applications

- Battery powered devices

- Core voltage

- Supply voltage sensitive circuits

- Power solutions

- Clocking systems

What’s Included?

- Schematic or NetList

- Abstract view (.lef and .lib files)

- Layout (optional)

- Verilog behavior model

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Power Management Unit IP core

An ESD efficient, Generic Low Power Wake up methodology in an SOC

D32PRO, scalable & royalty free 32-bit CPU

Who Needs 64-Bit or 8-Cores?

Seven Steps to Create a Formal IP Specification

Producing an Effective WLAN Prototyping Platform

Semiconductor IP FAQ

What is Power Management Unit?

Power Management Unit is a Power Management Unit IP core from NTLab listed on Semi IP Hub.

How should engineers evaluate this Power Management Unit?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Power Management Unit IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.