Ultra Low Power PMU - (2.18µW) - SilTerra 0.18 um

This macro-cell is an ultra low consumption Power Management Unit (PMU) core designed for Silterra 0.18µm C18G CMOS technology TO…

Overview

This macro-cell is an ultra low consumption Power Management Unit (PMU) core designed for Silterra 0.18µm C18G CMOS technology TO (thick oxide) and HP (thin oxide) process.

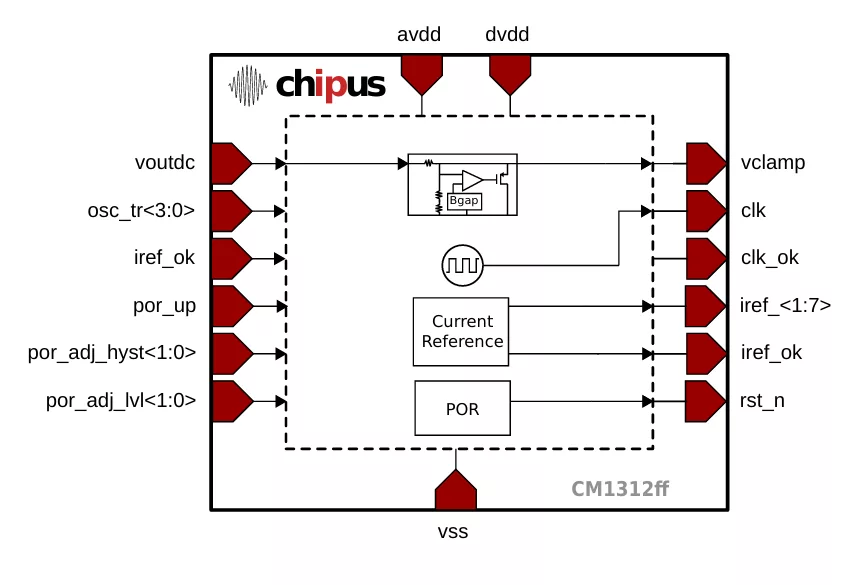

The circuit has a shunt regulator, internal voltage and bias current generators, built-in power-on-reset and oscillator.

The core is easily retargeted to any other CMOS technology with R-poly devices.

Key features

- Shunt regulator (1.8V)

- Current reference (15.5nA)

- Bandgapvoltage (1.17V)

- Built-in oscillator (2MHz, 600nA@1.2V)

- Biult-in POR

- Indicative area: 0.029mm2

Block Diagram

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| Silterra | 180nm | G | Silicon Proven |

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Power Management Unit IP core

An ESD efficient, Generic Low Power Wake up methodology in an SOC

D32PRO, scalable & royalty free 32-bit CPU

Who Needs 64-Bit or 8-Cores?

Seven Steps to Create a Formal IP Specification

Producing an Effective WLAN Prototyping Platform

Semiconductor IP FAQ

What is Ultra Low Power PMU - (2.18µW) - SilTerra 0.18 um?

Ultra Low Power PMU - (2.18µW) - SilTerra 0.18 um is a Power Management Unit IP core from Chipus Microelectronics listed on Semi IP Hub. It is listed with support for silterra Silicon Proven.

How should engineers evaluate this Power Management Unit?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Power Management Unit IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.