Power management unit (1.2 V output voltage, 945 nA output current)

065TSMC_PMU_01 is designed to supply embedded integrated circuits with stable and precise internal voltage and currents.

Overview

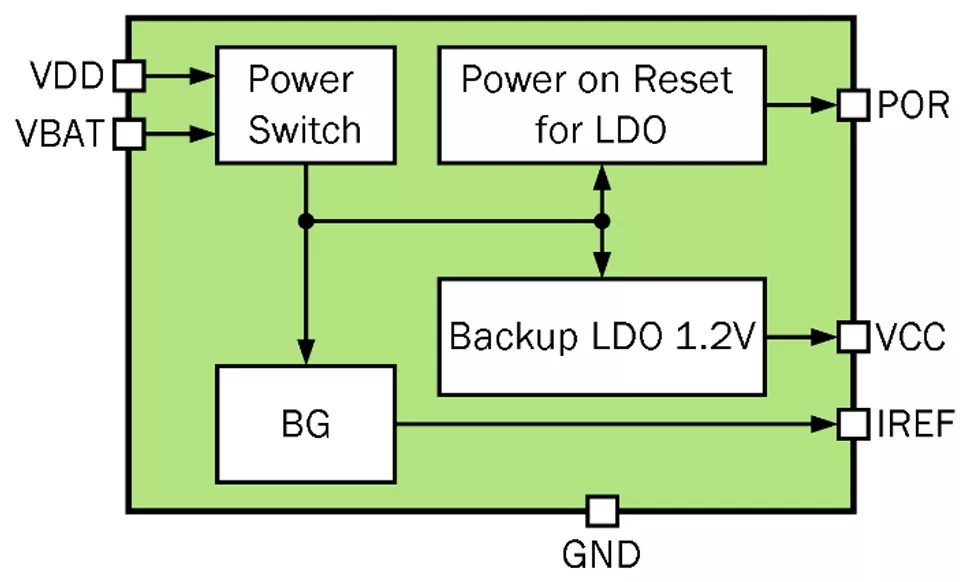

065TSMC_PMU_01 is designed to supply embedded integrated circuits with stable and precise internal voltage and currents. It integrates power switch element, LDO, Bangap and Power On Reset block. PMU have controllable input voltage level and are complemented with VDD detectors to monitor the input voltage value. Two modes are available: full power mode and battery mode. If IO power voltage enable then LDO supply powered by 2.5V, if IO power voltage disable then LDO supply powered by battery power. The voltage regulator consists of a differential amplifier which compares reference voltage with voltage from a feedback divider. It adjusts the impedance of a PMOS transistor for stabilization of output voltage at a set level. PMU have Power On Reset block which generate logic level signal to control LDO power supply.

Key features

- TSMC CMOS 65 nm

- Input voltage range from 0.9V to 2.8V

- Adjustable output voltage

- External output capacitor required

- Embedded power on reset module

- Low quiescent current

- Portable to other technologies (upon request)

Block Diagram

Applications

- Supply voltage sensitive circuits

- Battery-Powered equipment

- Power solutions

What’s Included?

- Schematic or NetList

- Abstract view (.lef and .lib files)

- Layout (optional)

- Verilog behavior model

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 65nm | GP | Silicon Proven |

Specifications

Identity

Provider

Learn more about Power Management Unit IP core

An ESD efficient, Generic Low Power Wake up methodology in an SOC

D32PRO, scalable & royalty free 32-bit CPU

Who Needs 64-Bit or 8-Cores?

Seven Steps to Create a Formal IP Specification

Producing an Effective WLAN Prototyping Platform

Semiconductor IP FAQ

What is Power management unit (1.2 V output voltage, 945 nA output current)?

Power management unit (1.2 V output voltage, 945 nA output current) is a Power Management Unit IP core from NTLab listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this Power Management Unit?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Power Management Unit IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.