OpenCAPI Synthesizable Transactor

The OpenCAPI Synthesizable Transactor is compliant with OpenCAPI TL V3.0, V3.1 and V4.0, OpenCAPI DL V1.0 and V1.5 Specifications…

Overview

The OpenCAPI Synthesizable Transactor is compliant with OpenCAPI TL V3.0, V3.1 and V4.0, OpenCAPI DL V1.0 and V1.5 Specifications and verifies OpenCAPI interfaces. OpenCAPI is build on top of it to make it robust. OpenCAPI Synthesizable Transactor provides a smart way to verify the OpenCAPI component of a SOC or a ASIC in Emulator or FPGA platform. OpenCAPI Synthesizable Transactor is developed by experts in networking, who have developed networking products in companies like Intel, Cortina-Systems, Emulex, Cisco. We know what it takes to verify a networking product.

Key features

- Compliant with OpenCAPI Transport layer Specification versions 3.0, 3.1 and 4.0.

- Compliant with OpenCAPI Data-link layer Specification versions 1.0 and 1.5.

- Complete OpenCAPI Tx/Rx functionality.

- Supports the Data Link Layer and Transaction Layer of OpenCAPI Specification.

- Supports the following Data-rates/speed

- 19.2 Gbps

- 20.0 Gbps

- 21.33 Gbps

- 25.78125 Gbps

- 25.6 Gbps

- 31.875 Gbps

- Supports PHY initialization.

- Supports DL training sets.

- Supports Lane reversal

- X8 or X4 Degraded Lane reversal

- X4 (when X4 is running on 8 lanes)

- Supports Degraded modes

- Odd lanes trained

- Even lanes trained

- Inside lanes trained

- Outside lanes trained

- Lane 1 trained

- Lane 0 trained

- Supports Deskew markers.

- Supports Endpoint link speed discovery.

- Supports Virtualisation.

- Supports AFU packets.

- Supports DLX packets.

- Supports DL packets.

- Supports Command ordering.

- Supports Translation ordering.

- Supports Write fragmentation 64, 128, 256 byte write operations

- Partial write operations

- 64, 128, 256 byte write operations

- Supports scrambler as in OpenCAPI specification.

- Scrambler can be enabled or disabled.

- Supports insertion of scrambler errors.

- Supports 64B/66B line encoding and decoding.

- Detects and reports the following errors

- Scrambler errors

- Under and oversize frame

- CRC errors

- Framing errors

- ACK errors

- Encoding/Decoding errors

- Training pattern errors

- Supports constraints Randomization.

- Status counters for various events on bus.

- Supports bus accurate timing and timing checks.

- OpenCAPI Verification IP comes with complete test suite to test every feature of OpenCAPI specification.

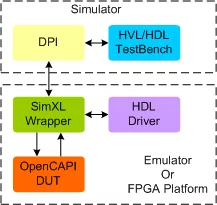

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the OpenCAPI testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CXL IP core

Powering Up Efficiency: A Deep Dive into CXL L0p and its Verification

Demystifying CXL Memory Interleaving and HDM Decoder Configuration

From GPUs to Memory Pools: Why AI Needs Compute Express Link (CXL)

cMPI: Using CXL Memory Sharing for MPI One-Sided and Two-Sided Inter-Node Communications

Boosting AI Performance with CXL

Frequently asked questions about CXL IP cores

What is OpenCAPI Synthesizable Transactor?

OpenCAPI Synthesizable Transactor is a CXL IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this CXL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CXL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.