NCO Intel® FPGA IP Core

A numerically controlled oscillator (NCO) is a digital signal generator, which synthesizes a discrete-time, discrete-valued repre…

Overview

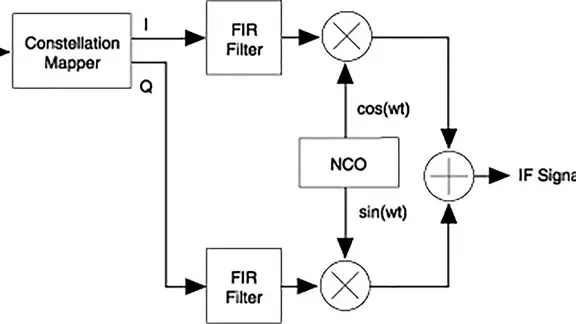

A numerically controlled oscillator (NCO) is a digital signal generator, which synthesizes a discrete-time, discrete-valued representation of a sinusoidal waveform. You can typically use NCOs in communication systems. In such systems, they are used as quadrature carrier generators in I-Q mixers, in which baseband data is modulated onto the orthogonal carriers in one of a variety of ways.

Key features

- 32-bit precision for angle and magnitude

- Source interface compatible with the Avalon® interface specification

- Multiple NCO architectures:

- Multiplier-based implementation using digital signal processing (DSP) blocks or logic elements (LEs), single cycle and multi-cycle

- Parallel or serial CORDIC-based implementation

- ROM-based implementation using embedded array blocks (EABs), embedded system blocks (ESBs), or external ROM

- Single or dual outputs (sine/cosine)

- Variable width frequency modulation input

- Variable width phase modulation input

- User-defined frequency resolution, angular precision, and magnitude precision

- Frequency hopping

- Multichannel capability

- Simulation files and architecture-specific testbenches for VHDL and Verilog HDL

- Dual-output oscillator and quaternary frequency shift keying (QFSK) modulator example designs

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Control Logic IP core

Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

A Comprehensive Post-Quantum Cryptography (PQC) Solution based on Physical Unclonable Function (PUF)

The Power of Shifting Left: Cadence Accelerating Innovation with Arm

Growing demand for high-speed data in consumer devices gives rise to new generation of low-end FPGAs

Why Hardware Root of Trust Needs Anti-Tampering Design

Frequently asked questions about Control Logic Accelerator IP cores

What is NCO Intel® FPGA IP Core?

NCO Intel® FPGA IP Core is a Control Logic IP core from Altera listed on Semi IP Hub.

How should engineers evaluate this Control Logic?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Control Logic IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.