100G UDP Offload Engine - Offloads UDP packet processing for efficient, high-speed networking

The 100G UDP Offload Engine in Verification IP (VIP) offloads UDP packet processing to specialized hardware, enhancing data trans…

Overview

The 100G UDP Offload Engine in Verification IP (VIP) offloads UDP packet processing to specialized hardware, enhancing data transmission efficiency. It ensures low latency and high throughput with support for checksum offloading, segmentation, and reassembly.

This solution is ideal for high-speed networks, including data centers, telecoms, and multimedia streaming. It supports both IPv4 and IPv6 protocols, delivering optimized performance for real-time applications, from gaming to AI/ML data transmission.

Key features

- Protocol Compliance Testing: Verifies that UDP packet transmission adheres to IPv4 and IPv6 protocol standards, ensuring correct header formatting and behavior. This helps guarantee reliable communication and proper interaction across diverse network environments.

- High-Speed Data Processing: Simulates UDP packet processing at speeds up to 100Gbps, ensuring that minimal latency is maintained during high-volume traffic scenarios. This is crucial for real-time applications and services requiring fast, uninterrupted data flow.

- Checksum Offloading: Offloads the calculation of UDP packet checksums to dedicated hardware, freeing up the CPU for other tasks and improving overall system performance. This reduces processing overhead, especially in high-speed network environments.

- Segmentation and Reassembly: Tests the fragmentation and reassembly of UDP packets to verify that larger payloads are correctly split and recombined during transmission. This ensures data integrity and proper handling of oversized UDP packets.

- Packet Generator and Checker: Generates specific traffic patterns for stress testing the network, simulating various traffic loads and packet sizes. The packet checker then verifies whether the generated packets match expected behavior for performance and compliance.

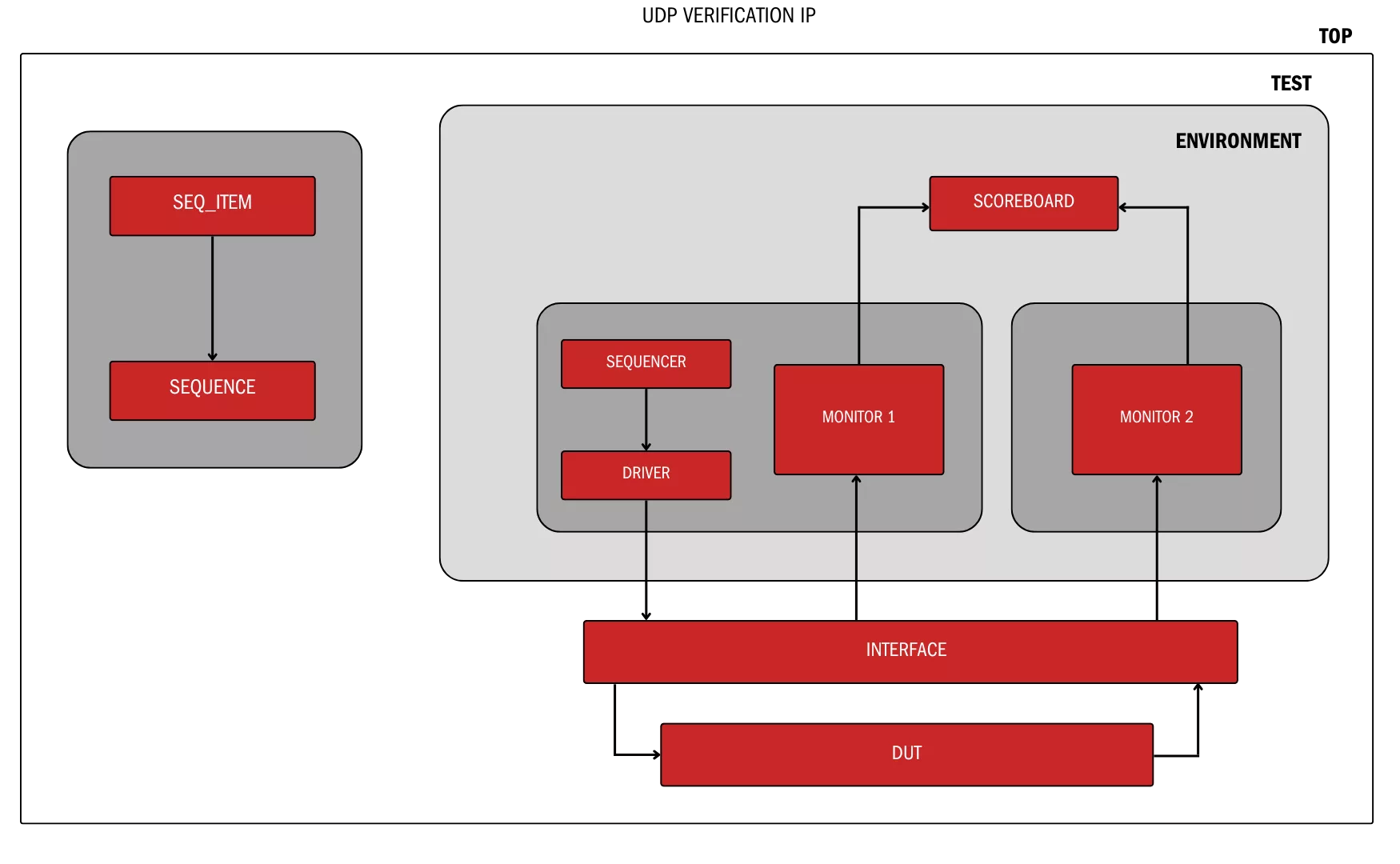

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Control Logic IP core

Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

A Comprehensive Post-Quantum Cryptography (PQC) Solution based on Physical Unclonable Function (PUF)

The Power of Shifting Left: Cadence Accelerating Innovation with Arm

Growing demand for high-speed data in consumer devices gives rise to new generation of low-end FPGAs

Why Hardware Root of Trust Needs Anti-Tampering Design

Frequently asked questions about Control Logic Accelerator IP cores

What is 100G UDP Offload Engine - Offloads UDP packet processing for efficient, high-speed networking?

100G UDP Offload Engine - Offloads UDP packet processing for efficient, high-speed networking is a Control Logic IP core from XtremeSilica listed on Semi IP Hub.

How should engineers evaluate this Control Logic?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Control Logic IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.