100G TCP/IP Offload Engine - Validates high-speed network traffic, optimizing flow and reliability

The 100G TCP/IP Offload Engine is a cutting-edge Verification IP designed to streamline the testing of high-speed networking inte…

Overview

The 100G TCP/IP Offload Engine is a cutting-edge Verification IP designed to streamline the testing of high-speed networking interfaces. It supports high-performance, real-world simulations of network traffic, flow control, and buffer management for seamless data integrity at 100G rates.

With its extensive debugging and protocol compliance features, the Offload Engine aids in reducing validation time while ensuring system reliability. It integrates easily with modern verification frameworks, optimizing performance across diverse network topologies

Key features

- High-Speed Data Handling: Simulates 100G data transmission to test network performance, ensuring compatibility with high-performance applications and maintaining optimal data flow. It validates adherence to TCP/IP standards for efficient data communication at ultra-high speeds.

- Checksum Offloading: Offloads checksum calculations for TCP, UDP, and IP protocols to network hardware, reducing CPU load and enhancing overall system performance. This results in lower latency and increased throughput by minimizing CPU intervention during packet transmission.

- Segmentation and Reassembly: Validates TCP Segmentation Offload (TSO) and large segment reassembly for efficient handling of large data packets in high-bandwidth networks. It ensures proper handling of packet fragmentation and reassembly across the network for smooth data transfer.

- Protocol Compliance: Ensures strict adherence to IPv4 and IPv6 standards, verifying correct implementation of essential protocol features. It also detects errors in feature implementation that could impact data transmission or network stability.

- Low-Latency Verification: Simulates low-latency data transfer to assess network performance in real-time applications, ensuring that round-trip times are optimized for applications requiring minimal delay. It helps improve the responsiveness of services like video conferencing and online gaming.

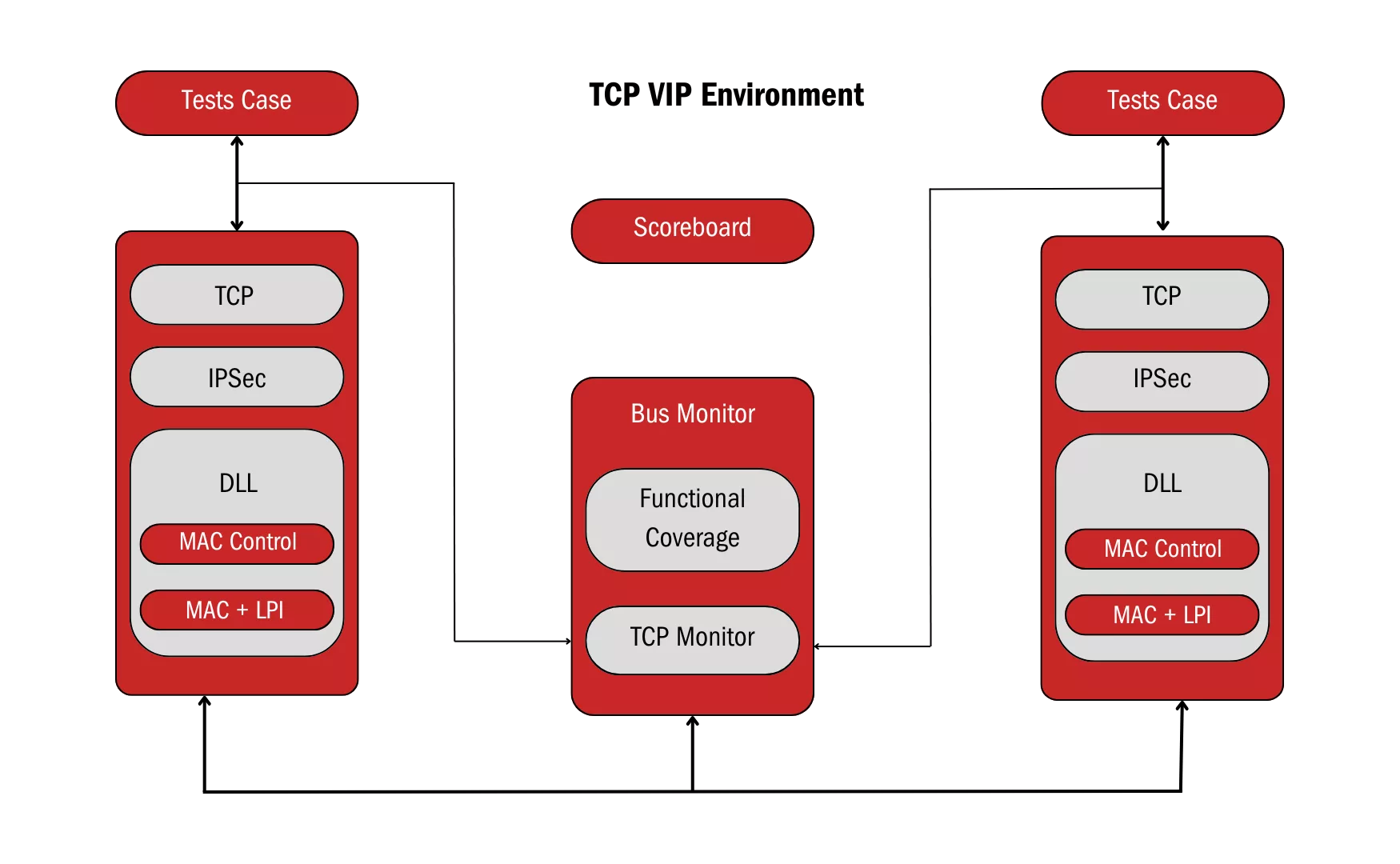

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Control Logic IP core

Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

A Comprehensive Post-Quantum Cryptography (PQC) Solution based on Physical Unclonable Function (PUF)

The Power of Shifting Left: Cadence Accelerating Innovation with Arm

Growing demand for high-speed data in consumer devices gives rise to new generation of low-end FPGAs

Why Hardware Root of Trust Needs Anti-Tampering Design

Frequently asked questions about Control Logic Accelerator IP cores

What is 100G TCP/IP Offload Engine - Validates high-speed network traffic, optimizing flow and reliability?

100G TCP/IP Offload Engine - Validates high-speed network traffic, optimizing flow and reliability is a Control Logic IP core from XtremeSilica listed on Semi IP Hub.

How should engineers evaluate this Control Logic?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Control Logic IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.