MIPI TWP Synthesizable Transactor

MIPI TWP Synthesizable Transactor provides a smart way to verify the MIPI TWP component of a SOC or a ASIC in Emulator or FPGA pl…

Overview

MIPI TWP Synthesizable Transactor provides a smart way to verify the MIPI TWP component of a SOC or a ASIC in Emulator or FPGA platform. MIPI TWP Synthesizable Transactor provides an smart way to verify the MIPI TWP bi-directional two-wire bus. The SmartDV's MIPI TWP Synthesizable Transactor is fully compliant with Specification for TWP version 1.0 and provides the following features.

Key features

- Compliant with MIPI TWP version 2.0 specification.

- Full MIPI Debug functionality.

- Supports all Debug CCC's and Opcodes

- Supports following three layer

- Layer T1: Flow Control. Supported by the TWP Padding Packet.

- Layer T2: Alignment Synchronization. Supported by the TWP Frame Synchronization Packet.

- Layer T3: Data. Supported by the TWP Frame

- Allows up to 111 source trace streams to be represented as a single stream and later separated by either hardware or software.

- Supports Error handling and flushing mechanism

- Fully synthesizable

- Static synchronous design

- Positive edge clocking and no internal tri-states

- Scan test ready

- Simple interface allows easy connection to microprocessor/microcontroller devices

- Supports on-the-fly protocol and data checking

- Ability to transmit strings to help verification of SOC

- Notifies the test bench of significant events such as transactions, warnings, and protocol violations

- MIPI TWP Synthesizable VIP comes with complete test suite to verify each and every feature of MIPI TWP specification

- Status counters for various events in bus

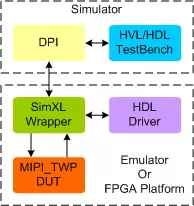

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the MIPI TWP testcases

- Examples showing how to connect various components, and usage of Synthesiable VIP

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about MIPI IP core

MIPI MPHY 6.0: Enabling Next-Generation UFS Performance

MIPI: Powering the Future of Connected Devices

Exploring the Latest Innovations in MIPI D-PHY and MIPI C-PHY

New Developments in MIPI's High-Speed Automotive Sensor Connectivity Framework

Streamlining Camera Security Validation Framework Using Synopsys MIPI CSE v2.0 VIP

Frequently asked questions about MIPI IP cores

What is MIPI TWP Synthesizable Transactor?

MIPI TWP Synthesizable Transactor is a MIPI IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this MIPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.