Simulation VIP for MIPI DSI-2

In production since 2008 on dozens of production designs.Cadence provides a mature and comprehensive Verification IP (VIP) for th…

Overview

In production since 2008 on dozens of production designs.

Cadence provides a mature and comprehensive Verification IP (VIP) for the DSI-2sm protocol, which is part of the MIPI® family. Incorporating the latest protocol updates, the mature and comprehensive Cadence® Verification IP for DSI-2sm Protocols provides a complete bus functional model (BFM), integrated automatic protocol checks, coverage model, and compliance tests. Designed for easy integration in testbenches at IP, system-on-chip (SoC), and system levels, the VIP for DSI-2 helps you reduce time to test, accelerate verification closure, and ensure end-product quality. Our VIP runs on all major simulators and supports SystemVerilog and e verification languages along with associated methodologies, including the Universal Verification Methodology (UVM) and Open Verification Methodology (OVM).

Supported Specification: MIPI for DSI v1.3.1, DSI2 v1.0, v1.1, DSI2 v2.0 and DPHY v1.2, v2.0, v2.1 and CPHY v1.1, and v1.

Key features

- Receiver and Transmitter Verification

- Verifies both DSI processor and peripheral

- Physical Layer

- Includes the MIPI D-PHYsm/C-PHYsm VIP for physical layer verification

- PHY Interfaces

- Serial and Parallel PHY interfaces

- Data Lanes

- 1 to 4 data lanes

- Power State

- High-Speed and Low Power data transmission

- LP Capabilities

- Ultra-Low Power mode (ULPM), triggers and LP data transmission

- Transmission of Multiple Packets

- Several merged packets in a single PHY transmission

- Traffic Modes

- Sending and receiving of DSI packets and frames in command mode and all video modes

- Accurate Video Mode Timing

- Generation and checks of accurate video mode timings

- Control of Payload Data

- User can control the frame and packet payload

- Scrambling

- Enables data scrambling in order to mitigate the effects of EMI and RF self-interference

- Built-In Test

- Supports PRBS test debug pattern for C-PHY

- Control Packet Data During BLLP Period

- Enables the user to control the packets that are sent during BLLP periods in non-VACT lines

- VESA Display Stream Compression Support

- Performs actual compression/decompression and provides a set of checkers for monitoring of DSC-related traffic

- Variable PPI HS Data Bus Width

- Supports 8-, 16-, and 32-bit PPI HS data bus widths over D-PHY 2.0

- Supports 16 and 32 PPI HS data bus widths over C-PHY

- DSI2 v 1.1

- Supports D-PHY specification 2.1 and C-PHY specification 1.2

- DSI2 Over D-PHY 2.1

- HS-Idle State, Alternate Calibration, and Preamble sequence

- DSI2 Over C-PHY 1.2

- ALP transactions and calibration sequence

- Video Frame for BTA and ULP during BLLP

- Supports sending and receiving BTA/ULP within video frame blanking period

- DSI2 v2.0 Data Types

- Data types SEP and PENP from Processor to Peripheral and vice versa and video frame data type PKT_PIXEL_STREAM_20_YCBCR422

- Video Command Mode Seamless Transactions

- Enables VIP to change command to video and video to command mode based on DCS command

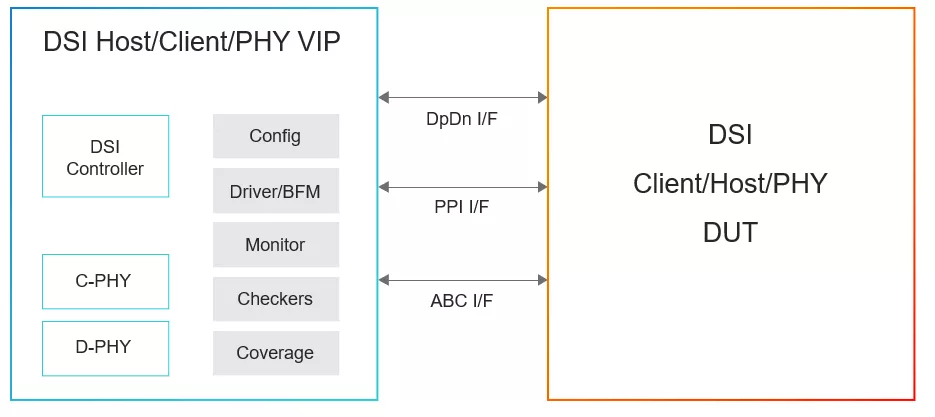

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about MIPI IP core

MIPI MPHY 6.0: Enabling Next-Generation UFS Performance

MIPI: Powering the Future of Connected Devices

Exploring the Latest Innovations in MIPI D-PHY and MIPI C-PHY

New Developments in MIPI's High-Speed Automotive Sensor Connectivity Framework

Streamlining Camera Security Validation Framework Using Synopsys MIPI CSE v2.0 VIP

Frequently asked questions about MIPI IP cores

What is Simulation VIP for MIPI DSI-2?

Simulation VIP for MIPI DSI-2 is a MIPI IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this MIPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.