MIPI STP Synthesizable Transactor

MIPI STP Synthesizable Transactor provides a smart way to verify the MIPI STP component of a SOC or a ASIC in Emulator or FPGA pl…

Overview

MIPI STP Synthesizable Transactor provides a smart way to verify the MIPI STP component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's MIPI STP Synthesizable Transactor is fully compliant with standard MIPI STP Specification and provides the following features.

Key features

- Compliant with MIPI STP Specification version 2.0 and 2.2

- Supports STP interface

- Supports ATB interface

- Supports TPIU interface

- Supports a trace stream comprised of 4-bit frames

- Supports for merging trace data from up to 65536 independent data sources (Masters)

- Supports up to 65536 independent data Channels per Master

- Supports basic trace data messages that can convey 4, 8, 16, 32, or 64 bit wide data

- Supports Time-stamped data packets using one of several time stamp formats including

- Gray code

- Natural binary

- Natural binary delta

- Export buffer depth (legacy STPv1 timestamp that requires DTC support)

- Supports Data packet markers to indicate packet usage by higher-level protocols

- Supports Flag packets for marking points of interest (for higher-level protocols) in the stream

- Supports Packets for aligning time stamps from different clock domains

- Supports Packets for indicating to the DTC the position of a trigger event, which is typically used to control actions in the DTC

- Supports Packets for cross-synchronization events across multiple STP sources

- Supports for user-defined data packets

- Facilities for synchronizing the trace stream on bit and message boundaries

- Supports all types of error insertion and detection

- Invalid Time-stamp format

- Invalid opcode

- Invalid async pattern

- Invalid version

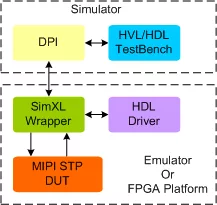

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the MIPI STP testcases

- Examples showing how to connect and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation also contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about MIPI IP core

MIPI MPHY 6.0: Enabling Next-Generation UFS Performance

MIPI: Powering the Future of Connected Devices

Exploring the Latest Innovations in MIPI D-PHY and MIPI C-PHY

New Developments in MIPI's High-Speed Automotive Sensor Connectivity Framework

Streamlining Camera Security Validation Framework Using Synopsys MIPI CSE v2.0 VIP

Frequently asked questions about MIPI IP cores

What is MIPI STP Synthesizable Transactor?

MIPI STP Synthesizable Transactor is a MIPI IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this MIPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.