MIPI SPMI Synthesizable Transactor

MIPI SPMI Synthesizable Transactor provides a smart way to verify the MIPI SPMI component of a SOC or a ASIC in Emulator or FPGA …

Overview

MIPI SPMI Synthesizable Transactor provides a smart way to verify the MIPI SPMI component of a SOC or a ASIC in Emulator or FPGA platform. MIPI SPMI Synthesizable Transactor provides an smart way to verify the MIPI SPMI bi-directional two-wire bus. The SmartDV's MIPI SPMI Synthesizable Transactor is fully compliant with versions 1.0 and 2.0 MIPI Alliance specification for System power management Interface and provides the following features.

Key features

- Supports 1.0 and 2.0 MIPI SPMI Specification

- Supports Full MIPI SPMI Master and Slave functionality

- Operates as a Master, Slave, or both

- Supports all topologies as per the MIPI SPMI specification

- Supports multiple slaves and multiple masters

- Compares read data with expected results

- Support for slave requests through Alert bit

- Support for slave request hold

- Supports following master bus connecting on bus

- Connecting by detecting SSC

- Connecting by detecting Bus idle

- Connecting by detecting Bus arbiration

- Supports following frames

- Command Frame

- Data/Address Frame

- No Response Frame

- Supports all types of SPMI commands

- Supports ACK/NACK generation as per 2.0 specs

- Supports various kind of Master and Slave errors generation

- Undefined command frame

- Command frame with parity error

- Command frame length error

- Address frame with parity error

- Data frame with parity error

- Read of unused register

- Write of an unused register

- Read using the broadcast ID or a GSID

- ACK/NACK errors

- Supports glitch monitor and injection

- Support injection of glitch at all positions of SDATA

- Support injection of glitch at all positions of SCLK

- Supports detection of glitches

- Supports extended register read/writes

- Supports optional signal also

- Supports device enumeration

- Supports master and slave arbitration

- Supports bus-accurate timing

- Supports half speed

- Status counters for various events in bus

- Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations

- MIPI SPMI Synthesizable Transactor comes with complete testsuite to test every feature of MIPI SPMI specification

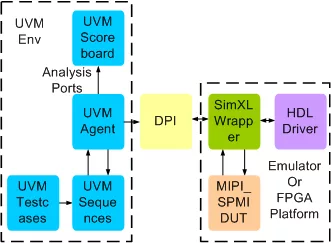

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the MIPI SPMI testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation also contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about MIPI IP core

MIPI MPHY 6.0: Enabling Next-Generation UFS Performance

MIPI: Powering the Future of Connected Devices

Exploring the Latest Innovations in MIPI D-PHY and MIPI C-PHY

New Developments in MIPI's High-Speed Automotive Sensor Connectivity Framework

Streamlining Camera Security Validation Framework Using Synopsys MIPI CSE v2.0 VIP

Frequently asked questions about MIPI IP cores

What is MIPI SPMI Synthesizable Transactor?

MIPI SPMI Synthesizable Transactor is a MIPI IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this MIPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.