MIPI D-PHY

D-PHY physical layer The IP for MIPI® D-PHYsm integrates a high-speed transmitter/receiver, low-power transmitter/receiver, and l…

Overview

D-PHY physical layer

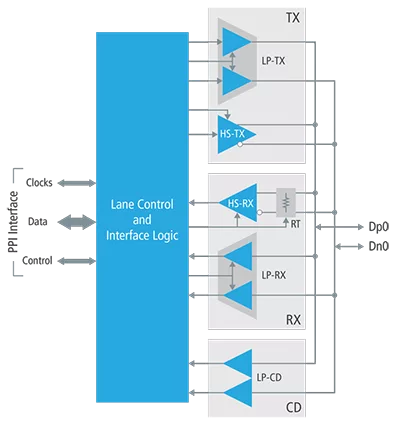

The IP for MIPI® D-PHYsm integrates a high-speed transmitter/receiver, low-power transmitter/receiver, and low-power contention detector that provide the full function of D-PHY. Our IP has an integrated PPI interface for ease-of-integration with MIPI CSI-2 and DSI controllers.

The IP for MIPI D-PHY provides lane flexibility with a compact and rectangular IP footprint, meeting usage models of modern SoCs. The pre-integrated CSI-2 and DSI solution ensures the interoperability and makes this PHY easy to integrate, shortening the product's time to market.

Key features

- Multiple Configurations Possible. TX-only (with integrated PLL), RX-only, and combined TX and RX configurations

- Complete Function for HS TX/RX, LP TX/RX, and LPCD with automatic termination control for high-speed and low-power modes

- Integrated BIST Capable of producing and checking PRBS, CRPAT, and CJTPAT

Block Diagram

Applications

- Automotive,

- Communications,

- Consumer Electronics,

- Data Processing,

- Industrial and Medical,

- Military/Civil Aerospace,

- Others

What’s Included?

- GDS II macros with abstract in LEF

- Verilog post-layout netlist

- STA scripts for use at chip or standalone PHY levels

- Liberty timing model

- SDF for back-annotated timing verification

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 7nm | N7+ | Silicon Proven |

Specifications

Identity

Provider

Learn more about MIPI PHY IP core

MIPI DPHY Solution

Infineon Drives Automotive MCU Performance Higher with Synopsys Interface IP

Cadence First to Demo Complete M-PCIe PHY and Controller Solution at MIPI and PCI-SIG Conferences

Super Edge Medical SoC (SEMC)

D-PHY, M-PHY & C-PHY? First Look at Testing MIPI's Latest PHY

Frequently asked questions about MIPI PHY IP

What is MIPI D-PHY?

MIPI D-PHY is a MIPI PHY IP core from Cadence Design Systems, Inc. listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this MIPI PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.