LVDS transmitter PHY

The LVDS transmitter is designed to support Single Link transmission between Host and Flat Panel Display with up to SXGA+ resolut…

Overview

The LVDS transmitter is designed to support Single Link transmission between Host and Flat Panel Display with up to SXGA+ resolution and Dual Link transmission between Host and Flat Panel Display with up to UXGA resolution.

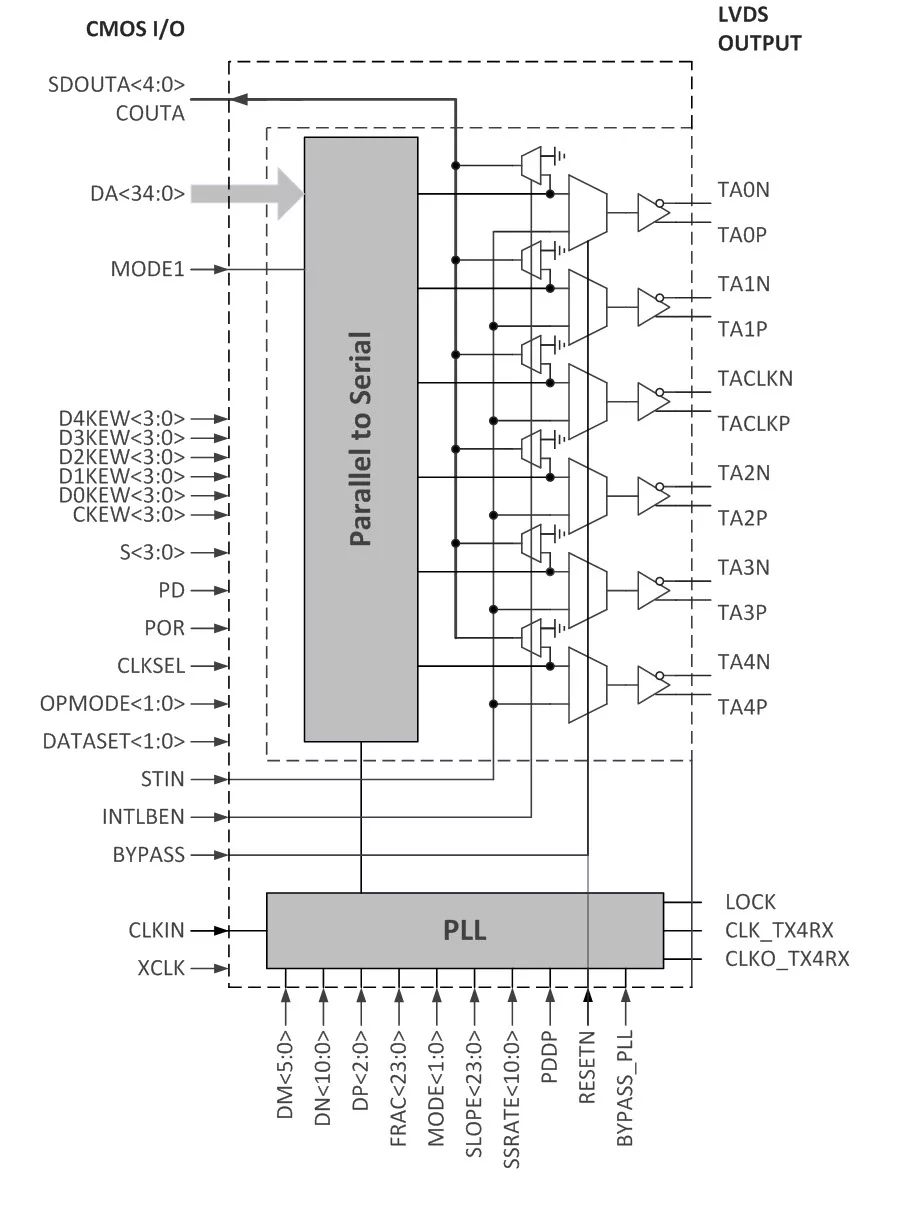

The IP converts 35-bit of CMOS/TTL data into LVDS data stream. The transmitter can be programmed for rising edge or falling edge clocks via a dedicated pin.

Key features

- Silicon Proven in 22,28,55,65,130n,180n from SMIC, Global Foundries and Samsung

- Compatible with the National DS90CF386

- Compatible with the TIA/EIA-644 standards

- Converts 35 bits data to 5-pair LVDS data stream

- Supports up to 1.05Gbps data rate for UXGA

- Clock edge selectable

- Wide dot clock range: 25 ~ 150MHz suited for VGA, SVGA, XGA, SXGA, SXGA+ and UXGA

- Output range is changeable from 50mV to 400mV

- Core area: 0.5430mm^2

- Power consumption:

- 175.4mW@1.05Gbps, prbs7 pattern

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is LVDS transmitter PHY?

LVDS transmitter PHY is a Single-Protocol PHY IP core from VeriSilicon Microelectronics (Shanghai) Co., Ltd. listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.