LIN Master Slave Controller

The vendor has designed LIN RTL IP Core, supporting data rate up to 20Kbps.

Overview

The vendor has designed LIN RTL IP Core, supporting data rate up to 20Kbps.

Local Interconnect Network (LIN) is a broadcasting, Single Master, and Multi Slave (up to 16) communication protocol designed to support those features where CAN is not required.

Key features

- LIN is a single wire-based interface, it reduces the cost and complexity of implementation.

- LIN is the best-suited and best alternative to CAN for applications that do not need high Bandwidth and that are of low speed.

- LIN is self-synchronized and therefore no need for external oscillators.

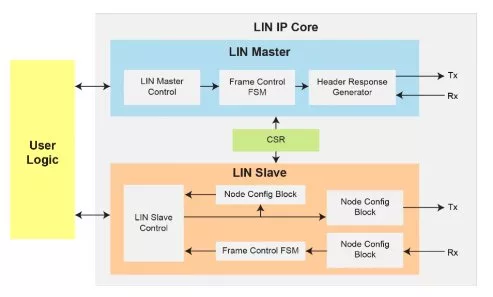

Block Diagram

Benefits

- LIN is a single wire-based interface, it reduces the cost and complexity of implementation.

- LIN is the best-suited and best alternative to CAN for applications that do not need high Bandwidth and that are of low speed.

- LIN is self-synchronized and therefore no need for external oscillators.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about LIN IP core

Understanding the LIN PHY (physical) layer

New opportunities for automotive LIN interfaces

VitaLLM: A Versatile and Tiny Accelerator for Mixed-Precision LLM Inference on Edge Devices

GenAI for Systems: Recurring Challenges and Design Principles from Software to Silicon

ChipBench: A Next-Step Benchmark for Evaluating LLM Performance in AI-Aided Chip Design

Frequently asked questions about LIN IP cores

What is LIN Master Slave Controller?

LIN Master Slave Controller is a LIN IP core from Logic Fruit Technologies listed on Semi IP Hub.

How should engineers evaluate this LIN?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this LIN IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.