Host / device LIN controller IP

The LIN Controllers IP– Local Interconnect Network Controllers IPs are compliant to LIN 2.0, 2.1 & 2.2A Specifications.

Overview

The LIN Controllers IP– Local Interconnect Network Controllers IPs are compliant to LIN 2.0, 2.1 & 2.2A Specifications. Backward compliant to LIN 1.3 Specification as well. These can be integrated into systems through various simple AMBA-APB, AMBA-AHB or SRAM like interfaces that require LIN connectivity commonly used in automotive and industrial applications.

The LIN Controller cores are easy to integrate with the rest of the system using either AMBA-APB, AMBA-AHB standard interfaces or other SRAM like simple interfaces. This highly configurable design supports programmable Interrupts, data and baud rates, acceptance filters & buffering schemes specific to the application.

Key features

LIN Specifications Support

- Implements the LIN 2.0, 2.1 and 2.2A protocols

- Backward Compatible to LIN 1.3

- Fully Programmable to operate in Host or Device Mode

- Simple interfaces to the system through AMBA-APB, AMBA-AHB or other SRAM like interfaces

- Design size can optionally be further reduced using another APB to fetch configurations information from outside

- Fully programmable data rates up to 20Kbits/s in Host Mode

- Automatic bit rate detection in register

- Configurable small data buffer

- Option for Clock synchronization

- Fully synchronous design

- Max. frequency supported up to 300MHz

- Optional Safety-enhanced ASIL & ISO26262 compliance design

Advanced Features

- Highly configurable design for data rate, baud-rate, interrupt sources and mix-bit options

- Very low software overhead, future-proof design

RAS Features

- Design supports enhanced checksum per channel

- Robust Interrupt structure for Error managements

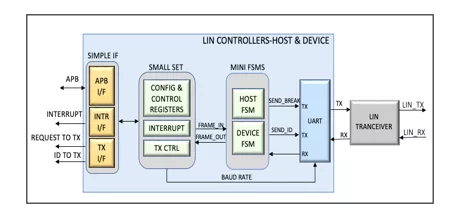

Block Diagram

Applications

- Automotive

- Industrial

What’s Included?

- System Verilog RTL Source Code

- A simplified Testbench with simulation models to run initial set of tests after release

- Synthesizable Netlist

- Synthesis Scripts and exception lists

- Timing Report

- Protocol Compliance & Coverage Report

- Sample Firmware with Drivers

- Application Notes

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about LIN IP core

Breaking the Silence: What Is SoundWire‑I3S and Why It Matters

UFS Goes Mainstream

Universal Flash Storage: Mobilize Your Data

Complete NAND Flash Solution: Logic, PHY and File System Software

Vertically Integrated MIPI Solutions

Frequently asked questions about LIN IP cores

What is Host / device LIN controller IP?

Host / device LIN controller IP is a LIN IP core from Arasan Chip Systems Inc. listed on Semi IP Hub.

How should engineers evaluate this LIN?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this LIN IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.