LIN Verification IP

Local Interconnect Network (LIN) is a single-wire, serial communication protocol based on the UART interface that is gaining popu…

Overview

Local Interconnect Network (LIN) is a single-wire, serial communication protocol based on the UART interface that is gaining popularity as a sub-bus standard in the automotive industry. LIN Verification IP are reusable components that provide ready made verification environment. Compatible with Local Interconnect Network (LIN) specifications versions 1.3,2.0,2,1,2.2A, ISO 17987-3 and ISO 17987-6. Supports all the frame types such as Unconditional, Event-triggered, Sporadic, Diagnostic and Reserved frames.

LIN 2.2A Verification IP includes an extensive test suite covering most of the possible scenarios. It can perform all protocal tests and moreover it allows an easy generation of very high number of patterns and a set of specified patterns to stress the DUT.

LIN Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

LIN Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Compatible with Local Interconnect Network (LIN) specification versions 1.3,2.0,2.1 and 2.2A.

- Compliant with ISO 17987-3 and ISO 17987-6.

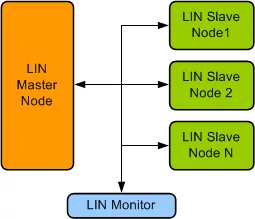

- Supports single Master and multiple Slaves.

- Supports test cases as per standard

- INTERNATIONAL STANDARD ISO 17987-6.

- Supports all frame types.

- Unconditional frames

- Event-triggered frames

- Sporadic frames

- Diagnostic frames

- Reserved frames

- Supports programmable clock frequency of operation.

- Simulates LIN cluster with number of nodes the user requires.

- These LIN nodes can be configured as Master or Slave nodes.

- The DUT can either be a LIN 2.2A master or slave device.

- Supports cluster go-to-sleep command, bus idle to sleep and wake up commands.

- Supports for segmented requests and segmented responses frames.

- Single Frame (SF)

- First Frame (FF)

- Consecutive Frames (CF)

- Supports for Node configuration handling.

- AssignNAD request message

- AssignNAD positive response message

- AssignFrameIdentifier request message

- AssignFrameIdentifier positive response message

- SaveConfiguration request message

- SaveConfiguration positive response message

- AssignFrameIdentifierRange request message

- AssignFrameIdentifierRange positive response message

- DataDump request message

- DataDump positive response message

- ReadByIdentifier request message

- ReadByIdentifier positive response message

- ReadByIdentifier negative response message

- Supports number of stop bits configuration.

- Supports the new break/sync field sequence detection.

- Supports all types of error insertion and detection

- Break length error

- Break delimiter error

- Sync start/stop error

- Sync pattern error

- PID start/stop error

- Parity error

- Data start/stop error

- Checksum start/stop error

- Checksum error

- Diagnostic frame errors

- Bit errors

- Master aborting in middle of transaction

- Header/Response timeout errors

- Segmented request/response frame errors

- Node configuration errors

- TBit width errors

- Supports Glitch insertion and detection

- Monitors, detects and notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- Functional safety features (B: No certification, with safety features, in line with the development process)

- Allows creation of both random and directed testcases as well as constraints randomization.

- Status counters for various events on bus.

- Supports callbacks in monitor, slave and master BFMs for user processing of data.

- LIN Verification IP comes with complete testsuite to test every feature of LIN specification.

- Functional coverage for all features of LIN.

Block Diagram

Benefits

- Faster testbench development and more complete verification of LIN designs.

- Easy to use command interface simplifies testbench control and configuration of slave and master.

- Simplifies results analysis.

- Integrates easily into Open Vera, SytemVerilog, Verilog and SystemC.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the LIN testcases.

- Examples showing how to connect various components, and usage of Master, Slave and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about LIN IP core

Understanding the LIN PHY (physical) layer

New opportunities for automotive LIN interfaces

VitaLLM: A Versatile and Tiny Accelerator for Mixed-Precision LLM Inference on Edge Devices

GenAI for Systems: Recurring Challenges and Design Principles from Software to Silicon

ChipBench: A Next-Step Benchmark for Evaluating LLM Performance in AI-Aided Chip Design

Frequently asked questions about LIN IP cores

What is LIN Verification IP?

LIN Verification IP is a LIN IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this LIN?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this LIN IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.